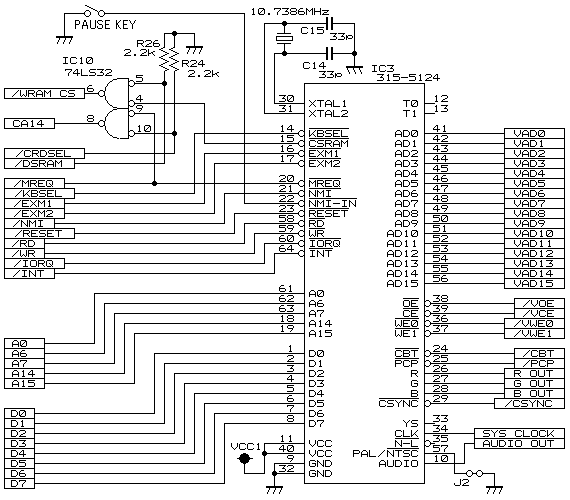

| CPU | D780C-1(Z80A) 3.579MHz |

| VDP | 315-5124 |

| PSG | SN76489(僐儞僷僠偱倁俢俹偵撪憼) |

| ROM | 僗儘僢僩偵傛傝嫙媼 |

| RAM | 8KB(奼挘壜) |

| V-RAM | 16KB |

俽俧亅侾侽侽侽乛II偺忋埵婡庬

倁俢俹傪斈梡偐傜愱梡僠僢僾偵偟偰僴乕僪僂僃傾僗僋儘乕儖傗

夋柺偺儅僗僋摍儕傾儖僞僀儉僎乕儉偵昁梫側傕偺偼偦傠偭偰偄傞

摿掕偺夋柺傪屌掕偟側偑傜僴乕僪僂僃傾僗僋儘乕儖偼偐側傝柺敀偄婡擻

奼挘俬乛俷億乕僩偼梡堄偝傟偰偄傞偑丄僼儖僨僐乕僪偝傟偰偍傜偢偦傟傎偳奼挘惈偑柍偄偺偑巆擮

傑偨僗僾儔僀僩偵斀揮婡擻偑柍偄偺傕偍偟偄強丄偦偺偐傢傝俛俧夋柺偺婡擻偑崅偄

挷傋傟偽挷傋傞傎偳儅僗僞乕僔僗僥儉偺僾儘僩僞僀僾偵巚偊偰偔傞乮僜儗偱崲傞栿偱傕柍偄偱偡偑乯

丂

丂

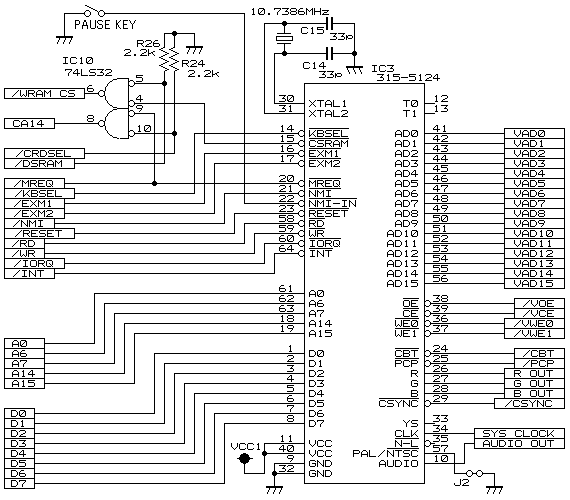

俠俹倀丗兪俹俢俈俉侽亅侾

丂

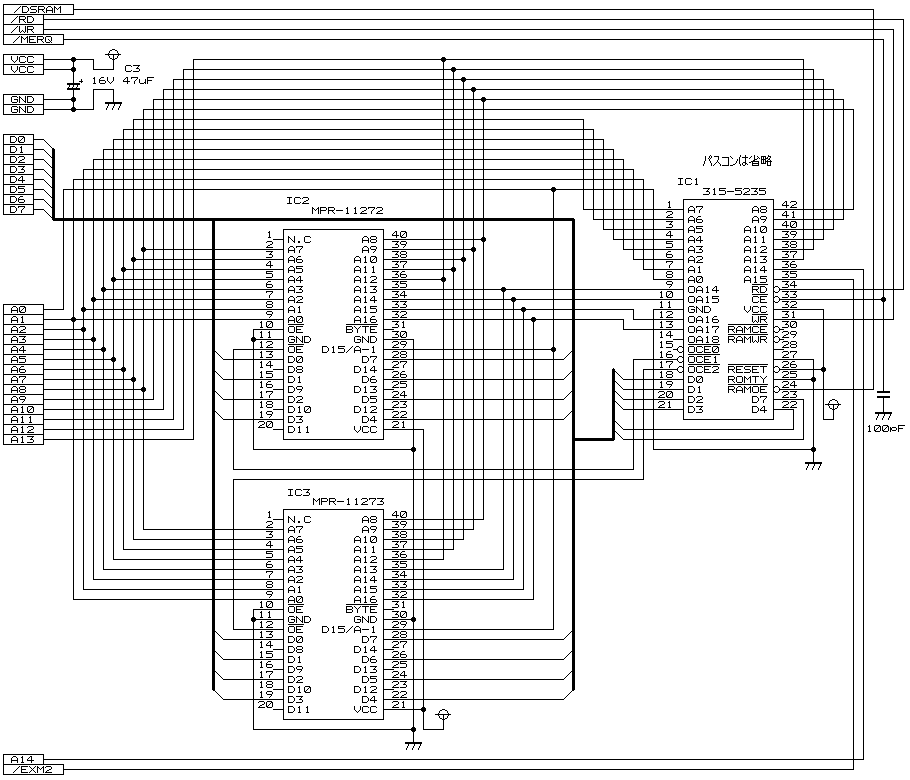

俶俤俠偺俹俢俈俉侽亅侾傪巊梡

僋儘僢僋偼10.7386俵俫倸傪俁暘廃偟偰栺3.579俵俫倸

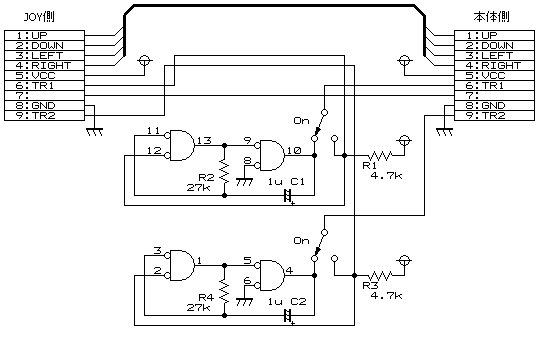

妱傝崬傒偼儌乕僪侾偱俶俵俬偼俹俙倀俽俤儃僞儞傪墴偣偽偐偐傝

俬俶俿偼倁俢俹乮倁亅俽倄俶俠偲俫亅俽倄俶俠乯偵妱傝摉偰傜傟偰偄傞丅

丂

丂

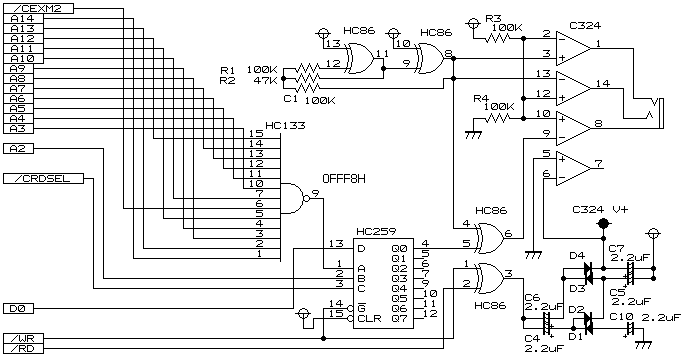

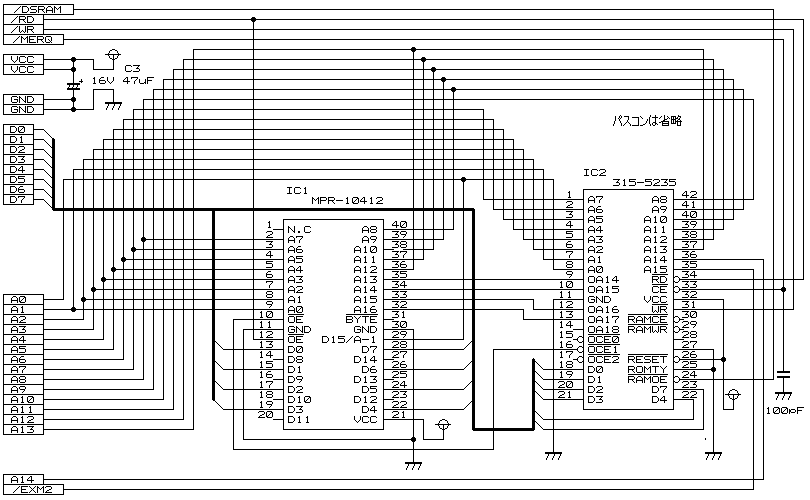

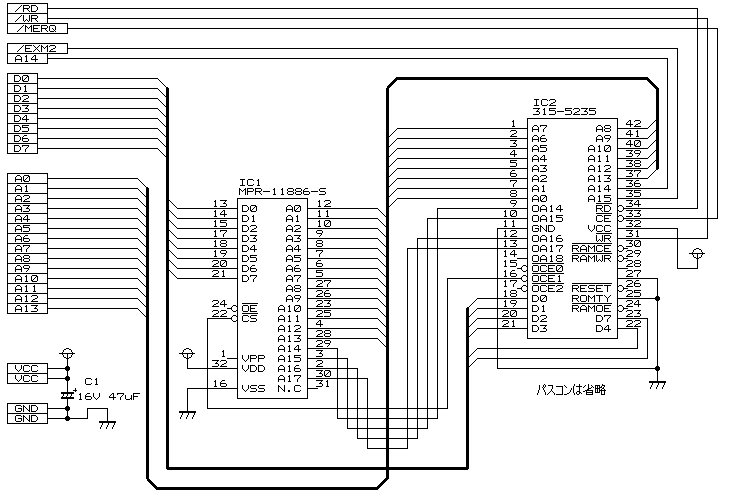

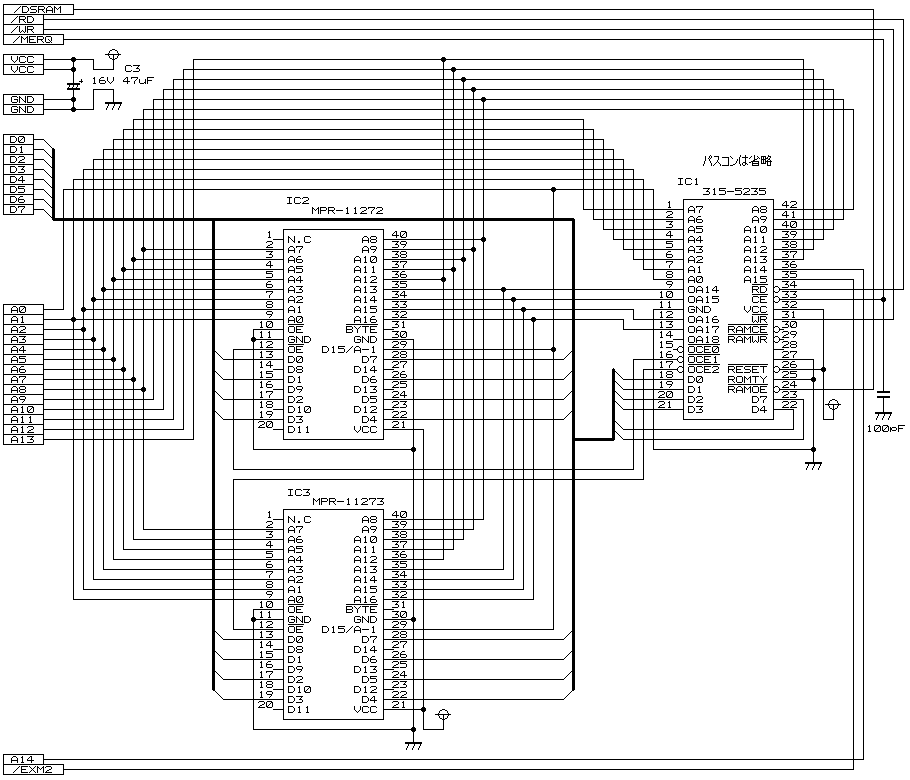

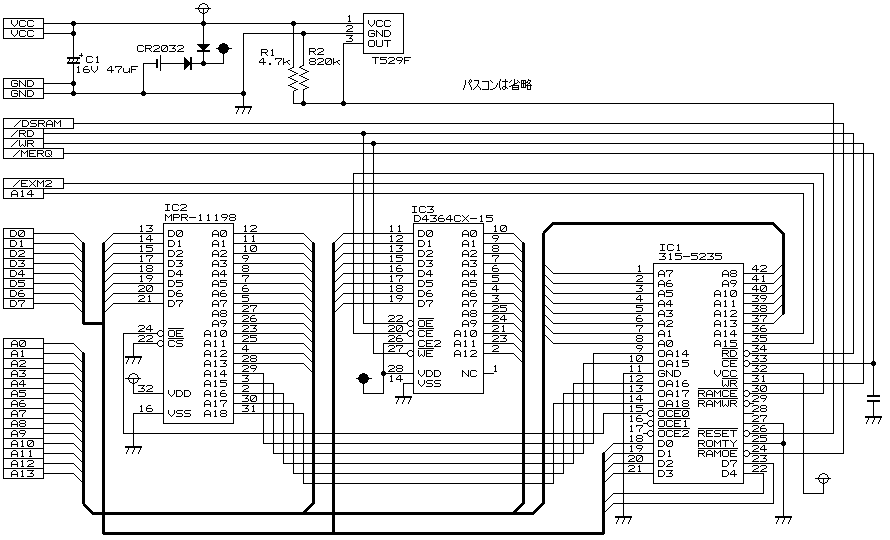

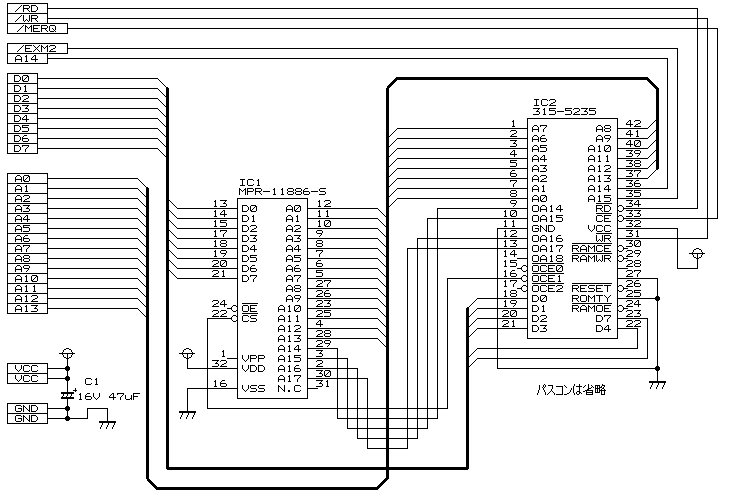

倁俢俹丗俁侾俆亅俆侾俀係

丂

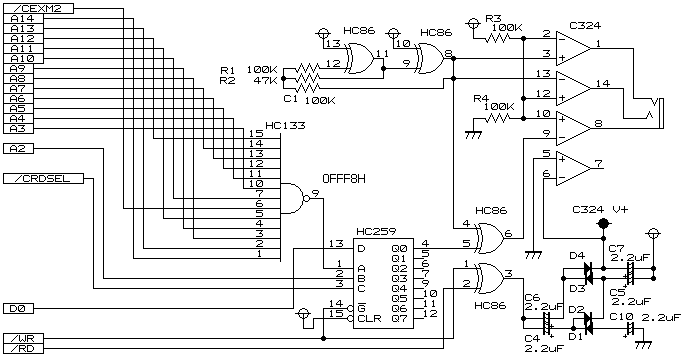

俁侾俆亅俆侾俀係偼儎儅僴惢偱傾僪儗僗僨僐乕僪丄俹俽俧摍傕偙偺僠僢僾偑扴摉丄

僴乕僪僂僃傾僗僋儘乕儖丄夋柺偺儅僗僋丄俛俧俇係怓32僷儗僢僩丄僗僾儔僀僩64怓32僷儗僢僩

慜偺婡庬偵巊梡偝傟偰偄傞俿俵俽亅俋俋侾俉傪戝暆偵夋柺偺儌乕僪傪奼挘偡傞丅

俿俵俽亅俋俋侾俉偲傎傏摨偠婡擻傕帩偮偑敪怓偑庒姳偪偑偆

丂

丂

俹俽俧丗俁侾俆亅俆侾俀係偵撪憼

丂

俽俧亅侾侽侽侽僔儕乕僘偵巊傢傟偨俽俶俈俇係俉俋偲僐儞僷僠偱倁俢俹偺僠僢僾偵撪憼

僋儘僢僋偼3.579俵俫倸

丂

丂

俼俷俵

丂

俼俷俵偼杮懱偵偼撪憼偝傟偰偍傜偢丄

僇乕僩儕僢僕枖偼僇乕僪偱嫙媼偡傞宍偲側傝傑偡

儊僈俼俷俵偼僇乕僩儕僢僕偺僠僢僾偱惂屼偝傟傞偨傔

杮懱扨懱偱偼僶儞僋愗傝懼偊摍偺婡擻偼偁傝傑偣傫丅

僶儞僋愗傝姺偊偺曽朄偼婎杮偼摑堦乮旕儔僀僙儞僗僜僼僩彍偔乯偝傟偄傑偡

丂

丂

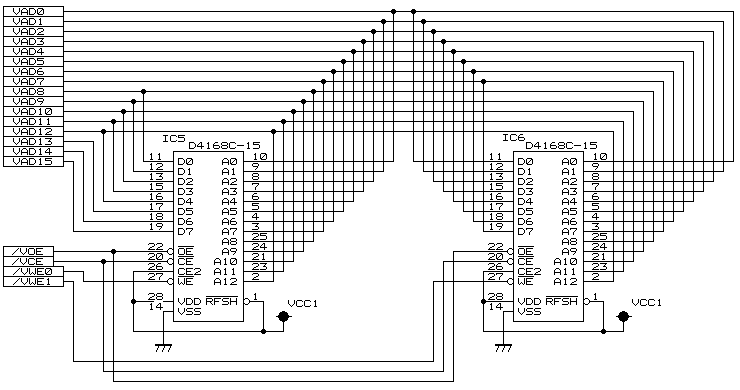

俼俙俵

丂

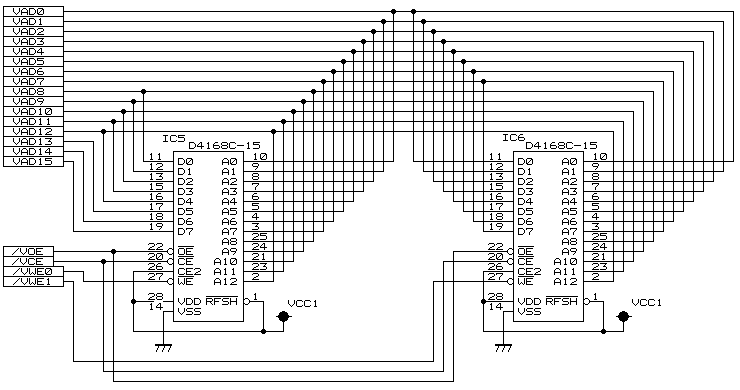

俼俙俵偼杮懱偵俉俲俛偑撪憼偝傟偰偄傑偡偑

僇乕僩儕僢僕偐傜杮懱撪憼偺俼俙俵傪巊梡嬛巭偵偡傞(俛俁傪侾偵偡傞)帠偑弌棃傑偡

怴偨偵俽亅俼俙俵傪杮懱撪俼俙俵偺戙傢傝偲偟偰巊梡弌棃傞傛偆偵愝寁偝傟偰偄傑偡

傑偨丄/俤倃俿侾偑侽俉侽侽侽俫偺乛俠俽偲側傝傑偡

傾僪儗僗偼侽俠侽侽侽俫乣侽俢俥俥俥俫偵攝抲偟偰偄傑偡

丂

丂

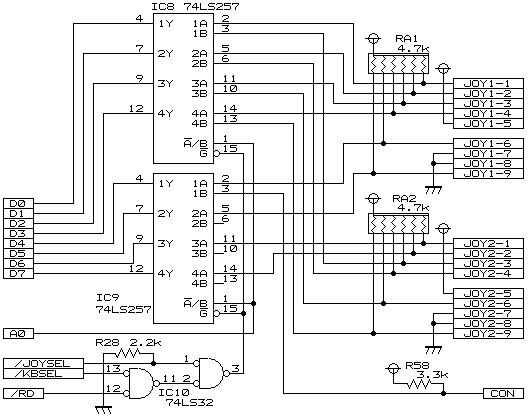

僎乕儉僊傾偱偼俽俵俽乛俧俧儌乕僪偺愗傝姺偊偼

僇乕僪儕僢僕撪偺僕儍儞僷偱愗傝姺偊傑偡

偦偺帪偵捠怣偺億乕僩傕巊梡傕愗傝姺傢傝俽俵俽儌乕僪偱偼巊梡弌棃側偔側傝

捠怣億乕僩偺僨乕僞偺曐帩偑弌棃側偔側傝傑偡

偦傟傪棙梡偟偰僎乕儉僊傾偺俬俹俴偱偼

俽俵俽儌乕僪偐俧俧儌乕僪偺敾抐傪峴偄傑偡

丂

丂

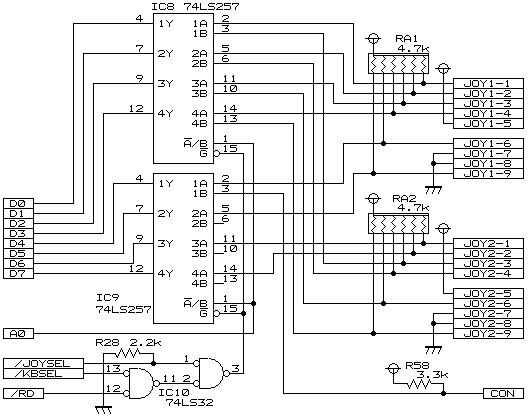

妱傝崬傒

丂

俵俙俼俲 III偵偼儌乕僪侾偱俀偮偺妱傝崬傒偑偁傝傑偡丅

丂侾丗倁俢俹偐傜敪惗偡傞丂丂丂丂丂丂丂乛俬俶俿

丂俀丗俹俙倀俽俤儃僞儞傪墴偡偲敪惗偡傞乛俶俵俬

丂

丂

乛俬俶俿偼倁俢俹丂俼仈00偲俼仈01偺俤俬侽丄俤俬侾偺慻傒崌傢偣偱

倁亅俽倄俶俠丄俫亅俽倄俶俠丄椉曽丄妱傝崬傒傪敪惗偝偣側偄係捠傝偑偁傝傑偡

乛俬俶俿側偺偱敪惗偡傞偲侽侽侽俁俉俫偵旘傃傑偡

偦偙偱倁亅俽倄俶俠偐俫亅俽倄俶俠偐偺敾抐傪偟偰奺妱傝崬傒儖乕僠儞偵旘傇偺偱偡偑

敾抐曽朄偼倁俢俹偺僗僥乕僞僗儗僕僗僞偺倓俈傪尒傞昁梫偑偁傝傑偡

丂侾側傜倁亅俽倄俶俠乮倁俛俴俙俶俲乯妱傝崬傒

丂侽側傜俫亅俽倄俶俠乮俫亅俴俬俶俤乯妱傝崬傒

丂

乛俶俵俬偼侽侽侽俇俇俫傊旘傃傑偡丅

丂

丂

僂僃僀僩

丂

俵俙俼俲丂III偼捠忢偺巊梡偱偼僲乕僂僃僀僩側偺偱偡偑

俹俽俧偺億乕僩傪彂偒崬傫偩応崌栺32僋儘僢僋暘偺僂僃僀僩偑偐偐傝傑偡乮枹妋擣乯

丂

丂

儅僗僞乕僔僗僥儉偲偺堘偄

丂

僇乕僩儕僢僕偲僇乕僪偲杮懱俼俙俵偺愗傝姺偊傪夞楬偺傒偱愗傝姺偊偰偄傞偺偑俵俙俼俲 III

俬俠丂俁侾俆亅俆俀俋俈偱億乕僩偱愗傝姺偊傞偺偑儅僗僞乕僔僗僥儉偵側傝傑偡

俁侾俆亅俆俀俋俈偺惂屼梡億乕僩侽俁俤俫丄侽俁俥俫偑捛壛偝傟偰

俰俷倄抂巕摍偺惂屼傕峴偄傑偡

偦傟偵敽偄億乕僩侽俢俠俫乣侽俢俥俫傕庒姳曄峏偑偝傟偰偄傑偡

丂

俁俢僔僗僥儉偺惂屼偵娭偟偰偼俵俙俼俲 III偼俛俀抂巕傪僆乕僾儞偵偟偰

俁俢傾僟僾僞偺僇乕僪抂巕傪婲摦弌棃傞傛偆偵偟偰

儅僗僞乕僔僗僥儉偼俁侾俆亅俆俀俋俈偱惂屼偟偰偄傑偡

丂

倁俢俹偼婲摦傑偱偵彮偟帪娫偑偐偐傝傑偡

俵俙俼俲 III偱偼嵟弶偵僂僃僀僩乮俀昩懸偮乯傪偐偗偰偐傜倁俢俹傪傾僋僙僗乮弶婜壔乯偟傑偡

僂僃僀僩傪偐偗偢偵倁俢俹傪傾僋僙僗偟傑偡偲夋柺偵偼壗傕昞帵偝傟側偄傑傑偵側傝傑偡

儅僗僞乕僔僗僥儉偼俬俹俴偑婲摦偟偰僂僃僀僩傪偐偗偰偐傜

奜晹僜僼僩偑婲摦偡傞偺偱昁梫偁傝傑偣傫

丂

丂

抂巕恾

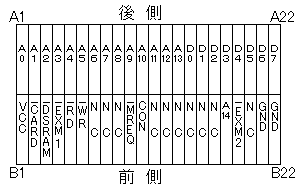

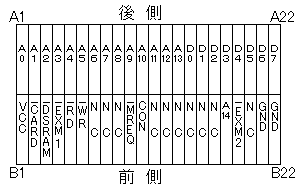

俙侽乣俙侾係丗傾僪儗僗丂僶僗

俢侽乣俢俈 丗僨乕僞丂丂僶僗

乛俠俙俼俢丂丗俠俙俼俢僗儘僢僩偺巊梡丂侾亖巊梡晄壜丄侽亖巊梡壜

乛俢俽俼俙俵丗杮懱撪偺俼俙俵偺巊梡丂丂侾亖巊梡晄壜丄侽亖巊梡壜

乛俤倃俵侾丂丗侽俉侽侽侽俫偺俠俽乮晧椣棟乯

乛俤倃俵俀丂丗侽侽侽侽侽俫偺俠俽乮晧椣棟乯

俠俷俶丂丂丂丗奼挘僐僱僋僞偺18僺儞偲捈寢

丂

俛俀乮乛俠俙俼俢乯偼捠忢偺僎乕儉偺偲偒偼

倁俠俠偲僔儑乕僩偝傟偰偄偰俁俢僌儔僗巊梡壜擻僜僼僩偱俶丏俠丏偲側偭偰偄傑偡

偦偺堊俁俢僌儔僗懳墳偺僎乕儉偲僇乕僪偺僎乕儉傪巋偟側偑傜偩偲

僶僗嫞憟偡傞嫲傟偑偁傝傑偡

乛俠俙俼俢偼俵俙俼俲 III愱梡偺抂巕偱偡乮婡庬偛偲偵堘偄偑偁傝傑偡乯

丂

丂

奼挘抂巕恾

俙侽乣俙侾係丗傾僪儗僗丂僶僗

俢侽乣俢俈 丗僨乕僞丂丂僶僗

乛俠俙俼俢丂丗俠俙俼俢僗儘僢僩偺巊梡丂侾亖巊梡晄壜丄侽亖巊梡壜

乛俢俽俼俙俵丗杮懱撪偺俼俙俵偺巊梡丂丂侾亖巊梡晄壜丄侽亖巊梡壜

乛俤倃俵侾丂丗侽俉侽侽侽俫偺俠俽乮晧椣棟乯

乛俤倃俵俀丂丗侽侽侽侽侽俫偺俠俽乮晧椣棟乯

俠俷俶丂丂丂丗奼挘僐僱僋僞偺18僺儞偲捈寢

丂

俛俀乮乛俠俙俼俢乯偼捠忢偺僎乕儉偺偲偒偼

倁俠俠偲僔儑乕僩偝傟偰偄偰俁俢僌儔僗巊梡壜擻僜僼僩偱俶丏俠丏偲側偭偰偄傑偡

偦偺堊俁俢僌儔僗懳墳偺僎乕儉偲僇乕僪偺僎乕儉傪巋偟側偑傜偩偲

僶僗嫞憟偡傞嫲傟偑偁傝傑偡

乛俠俙俼俢偼俵俙俼俲 III愱梡偺抂巕偱偡乮婡庬偛偲偵堘偄偑偁傝傑偡乯

丂

丂

奼挘抂巕恾

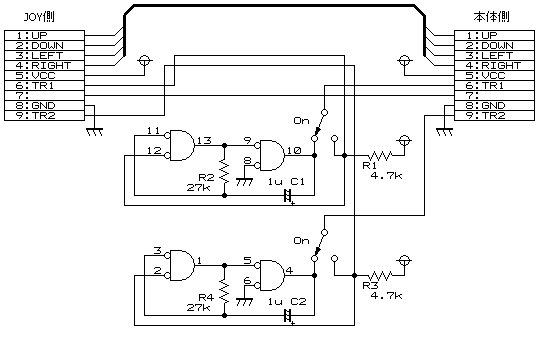

俥俵壒尮儐僯僢僩傗僉乕儃乕僪俽俲亅侾侾侽侽偺愙懕抂巕偱偡

乛俰俷倄俽俤俴偼僕儑僀僗僥傿僋廃傝偲楢摦偟偰偍傝

乛俰俷倄俽俤俴丄乛俲俛俽俤俴丄乛俼俢偺俁偮偑侽側傜俰俷倄抂巕偑巊梡壜擻偵側傝傑偡

俛侾侾偼俽俲亅侾侾侽侽偩偲俹俛係丄杮懱偩偲僇僙僢僩抂巕偺俛侾侾偵宷偑偭偰偍傝

億乕僩偺侽俢俢俫偺倓係偱忬懺偑擿偔偙偲偑弌棃傑偡丅

丂

丂

儊儌儕丂儅僢僾

俥俵壒尮儐僯僢僩傗僉乕儃乕僪俽俲亅侾侾侽侽偺愙懕抂巕偱偡

乛俰俷倄俽俤俴偼僕儑僀僗僥傿僋廃傝偲楢摦偟偰偍傝

乛俰俷倄俽俤俴丄乛俲俛俽俤俴丄乛俼俢偺俁偮偑侽側傜俰俷倄抂巕偑巊梡壜擻偵側傝傑偡

俛侾侾偼俽俲亅侾侾侽侽偩偲俹俛係丄杮懱偩偲僇僙僢僩抂巕偺俛侾侾偵宷偑偭偰偍傝

億乕僩偺侽俢俢俫偺倓係偱忬懺偑擿偔偙偲偑弌棃傑偡丅

丂

丂

儊儌儕丂儅僢僾

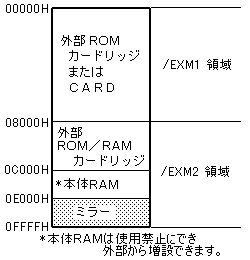

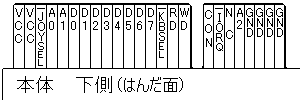

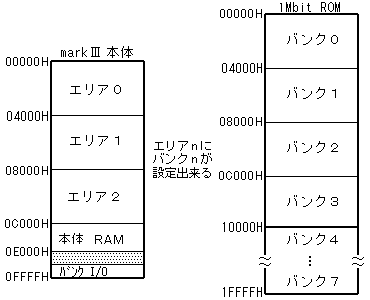

俼俷俵僄儕傾偼僇乕僪丄僇乕僪儕僢僕偵傛偭偰梕検偑曄傝傑偡

侽俉侽侽侽俫偵偼俼俙俵傗俼俷俵傪嵹偣傞偙偲偑偱偒傑偡丅

杮懱撪偺俼俙俵偼俛俁抂巕傪侾偵偡傞帠偵傛偭偰巊梡嬛巭偵弌棃傑偡乮儅僗僞乕僔僗僥儉偼峏偵僜僼僩偱愗傝姺偊壜乯

儅僗僞乕僔僗僥儉偵偼俁偮偺僗儘僢僩乮僇乕僩儕僢僕丄僇乕僪丄奼挘抂巕乯偵傛偭偰儊儌儕傪嵹偣傞帠偑弌棃傑偡

僗儘僢僩偺愗傝姺偊偼億乕僩侽俁俤俫傪巊梡偟偰偄傑偡偑俵俙俼俲丂III偱偼億乕僩傪擿偄偰傕侽俥俥俫偵側傝傑偡

儅僗僞乕僔僗僥儉偱偼俬俹俴婲摦丄僗儘僢僩僠僃僢僋丄愗傝姺偊偱巊梡偟偨億乕僩侽俁俤俫偺撪梕偑

侽俠侽侽侽俫偵弌椡丄棙梡偟傑偡乮儅僗僞乕僔僗僥儉偺傒乯

丂

儊僈俼俷俵偼儊儌儕儅僢僷傪僇乕僩儕僢僕撪偵帩偪杮懱撪偵偼僶儞僋愗傝姺偊偺婡擻偼偁傝傑偣傫

傑偨婔偮偐偺儊儌儕儅僢僷偑偁傝傑偡偑惂屼偺曽朄偼偳偺僇乕僩儕僢僕傕傎傏摨偠偱

僶儞僋愗傝懼偊曽幃偱儊儌儕儅僢僾丒霓丒俬乛俷偵傛偭偰惂屼偝傟傑偡

傾僪儗僗偼侽俥俥俥俠俫乣侽俥俥俥俥俫傑偱巊梡偟偰偍傝丄侾俇俲俛偛偲愗傝懼傢傝傑偡

丂

俁俢傾僟僾僞偼侽俥俥俥俉俫乣侽俥俥俥俛俫偺斖埻偱

僜僼僩偱偼侽俥俥俥俛俫傪巊梡偟偰偄傑偡乮懠偺傾僪儗僗偼儈儔乕乯

僼儖僨僐乕僪偼偝傟偰偄側偄偺偱杮懱撪偺儚乕僋俼俙俵偺侽俢俥俥俠俫乣侽俢俥俥俥俫偼

巊梡弌棃傑偣傫乮儅僢僷偺儈儔乕偵側偭偰偄傑偡乯

丂

丂侽俥俥俥俉俫乣侽俥俥俥俛俫丗俁俢僔僗僥儉偱巊梡 捠忢侽俥俥俥俛俫偺傒巊梡乮倓侽偱嵍丄塃偺愗傝懼偊丠)

丂侽俥俥俥俠俫丂丂丂丂丂丂丂丗庡偵僶僢僋傾僢僾俼俙俵偺愗傝姺偊

丂侽俥俥俥俢俫丂丂丂丂丂丂丂丗杮懱偺侽侽侽侽侽俫乣侽俁俥俥俥俫偵僶儞僋傪慖戰

丂侽俥俥俥俤俫丂丂丂丂丂丂丂丗杮懱偺侽係侽侽侽俫乣侽俈俥俥俥俫偵僶儞僋傪慖戰

丂侽俥俥俥俥俫丂丂丂丂丂丂丂丗杮懱偺侽俉侽侽侽俫乣侽俛俥俥俥俫偵僶儞僋傪慖戰

丂

丂

俬乛俷億乕僩

丂

倁俢俹撪偱億乕僩惂屼傪峴偭偰偍傝

巊梡傾僪儗僗僶僗偼俙侾俆丆俙侾係丄俙俈丄俙俇丄俙侽偟偐宷偑偭偰偍傜偢

俙侾俆丄俙侾係偼乛俤倃俵侾丄俀梡偱丄俙俈丄俙俇丄俙侽偑億乕僩梡偵側傝傑偡

偟偨偑偭偰億乕僩偼侽係侽俫偛偲嬫愗傜傟傑偡

奼挘僐僱僋僞偵偼乛俲俛俽俤俴偲俙侽乣俙俀偑偁傞偺偱

億乕僩侽俠侽俫埲崀偺億乕僩偼壓埵係價僢僩偼侽乣俈傑偱惂屼偱偒傑偡丅

丂侽侽侽俫乣侽俁俥俫丗僐儞僩儘乕儖乮枹巊梡乯

丂侽係侽俫乣侽俈俥俫丗俹俽俧乛倁俢俹

丂侽俉侽俫乣侽俛俥俫丗倁俢俹

丂侽俠侽俫乣侽俥俥俫丗俰俷倄抂巕乛奼挘僐僱僋僞乮俥俵亅俈侽丄俽俲亅侾侾侽侽乯

丂

侽俁俤俫丗俵俙俼俲丂III偱偼枹巊梡

丂俵俙俼俲丂III偱偼僇乕僩儕僢僕偲僇乕僪偺暪梡丄杮懱撪俼俙俵偲奼挘俼俙俵乮侽俠侽侽侽俫埲崀乯偺巊梡傪

丂夞楬偱嬛巭傪寛傔偰偄傑偡偑儅僗僞乕僔僗僥儉埲崀偱偼偙偺億乕僩傪巊梡偟偰

丂僇乕僩儕僢僕傗杮懱撪俼俙俵偺愗傝姺偊摍傪峴偄傑偡

丂億乕僩侽俁俤俫偲億乕僩侽俁俥俫偑俵俙俼俲丂III偲儅僗僞乕僔僗僥儉偺戝偒側堘偄偵側傝

丂僴乕僪傛傝側偺偑俵俙俼俲丂III丄僜僼僩傛傝偱億乕僩侽俁俤俫偲億乕僩侽俁俥俫傪巊梡偡傞偺偑儅僗僞乕僔僗僥儉偲偄偊傑偡丅

丂俵俙俼俲丂III偱偼枹巊梡側偺偱僨乕僞曐帩偝傟偰偄側偄偺偱偡偑撉傓偨傃偵僨乕僞偑曄壔偟傑偡

丂儅僗僞乕僔僗僥儉偱偼巊梡偟偰偄傑偡偑彂偒崬傒梡億乕僩側偺偱撉傓偲侽俥俥俫偵側傝傑偡

丂偦偺堊偵儅僗僞乕僔僗僥儉婲摦偺僗儘僢僩僠僃僢僋偱億乕僩侽俁俤俫偑儚乕僋侽俠侽侽侽俫偺撪梕偵側傝

丂俥俵壒尮傪巊梡偡傞応崌偵偙偺侽俠侽侽侽俫傪撉傫偱億乕僩侽俁俤俫乮俰俷倄抂巕嬛巭乯偵偡傞帠偱

丂傾僋僙僗偡傞帠偵側傝傑偡

丂

侽俁俥俫丗俵俙俼俲丂III偱偼枹巊梡

丂丂丂丂丂儅僗僞乕僔僗僥儉偱偼儊儌儕丄俰俷倄抂巕乛俥俵儐僯僢僩偺惂屼傪峴偄傑偡

丂

侽俈俤俫丗尰嵼偺倁僇僂儞僞乕乮擖椡乯

侽俈俥俫丗尰嵼偺俫僇僂儞僞乕乮擖椡乯乛俹俽俧乮弌椡乯

丂

侽俛俤俫乣侽俛俥俫丗倁俢俹

丂

億乕僩侽俠侽俫乣侽俠侾俫丗俰俷倄抂巕乮儈儔乕乯

丂僨僐乕僪偝傟偰偄側偄偺偱億乕僩侽俢俠俫乣侽俢俢俫偺儈儔乕偵側傝傑偡乮奼挘抂巕偵壗傕宷偘側偄応崌乯

丂晄巚媍側偍忛僺僢僩億僢僩偱偼億乕僩侽俠侽俫乣侽俠侾俫傪巊梡偟偰偄傑偡

丂偨偩偟俥俵儐僯僢僩傪晅偗偰偄傞応崌偼摦嶌偑偍偐偟偔側偭偰偟傑偆偺偱巊梡偟側偄曽偑椙偄偱偡

丂

侽俢俠俫丗俰俷倄抂巕乮擖椡乯

丂倓俈丗俰俷倄俀丂俀僺儞乮俢俷倂俶丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俇丗俰俷倄俀丂侾僺儞乮倀俹丂丂丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俆丗俰俷倄侾丂俋僺儞乮俀儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓係丗俰俷倄侾丂俇僺儞乮侾儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俁丗俰俷倄侾丂係僺儞乮俼俬俧俫俿乯丂侾亖僆僼丄侽亖僆儞

丂倓俀丗俰俷倄侾丂俁僺儞乮俴俤俥俿丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侾丗俰俷倄侾丂俀僺儞乮俢俷倂俶丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侽丗俰俷倄侾丂侾僺儞乮倀俹丂丂丂乯丂侾亖僆僼丄侽亖僆儞

丂

侽俢俢俫丗俰俷倄抂巕亄俠俷俶抂巕乮擖椡乯

丂倓俈丗俬俠俋丂俈係俴俽俀俆俈偺13僺儞丂侾偱屌掕乮枹巊梡乯

丂倓俇丗俬俠俋丂俈係俴俽俀俆俈偺10僺儞丂侾偱屌掕乮枹巊梡乯

丂倓俆丗俬俠俋丂俈係俴俽俀俆俈偺俇僺儞丂侾偱屌掕乮枹巊梡乯

丂倓係丗俠俷俶抂巕丂丂丂丂丂丂丂丂丂丂丂侾亖僆僼丄侽亖僆儞

丂倓俁丗俰俷倄俀丂俋僺儞乮俀儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俀丗俰俷倄俀丂俇僺儞乮侾儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侾丗俰俷倄俀丂係僺儞乮俼俬俧俫俿乯丂侾亖僆僼丄侽亖僆儞

丂倓侽丗俰俷倄俀丂俁僺儞乮俴俤俥俿丂乯丂侾亖僆僼丄侽亖僆儞

丂

丂仏億乕僩侽俢俢俫傪傒偰擔杮偺僴乕僪偐奀奜偺僴乕僪偑敾抐弌棃傑偡

丂丂億乕僩侽俁俥俫偵侽俥俆俫傪弌椡偟偰億乕僩侽俢俢俫傪尒傞

丂丂億乕僩侽俁俥俫偵侽俆俆俫傪弌椡偟偰億乕僩侽俢俢俫傪尒傞帠偱敾抐弌棃傑偡丅

丂丂丂俵俙俼俲丂III偺応崌

丂丂丂丂億乕僩侽俁俥俫偼巊梡偟偰偄側偄偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈乣俇偼侾侾偱屌掕

丂

丂丂丂擔杮偺儅僗僞乕僔僗僥儉偺応崌

丂丂丂丂億乕僩侽俁俥俫偺倓俁乣侾偺撪梕偼侽側偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈乣俇偼俀夞偲傕侽侽

丂

丂丂丂奀奜偺儅僗僞乕僔僗僥儉偺応崌

丂丂丂丂俰俷倄抂巕偺俈僺儞偺愝掕偺抣偑擖傞偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈亅俇偼侾侾偲侽侽

丂

丂丂丂侾侾偐傜侾侾側傜俵俙俼俲丂III

丂丂丂侽侽偐傜侽侽側傜擔杮偺儅僗僞乕僔僗僥儉

丂丂丂侾侾偐傜侽侽偵曄壔偡傞側傜奀奜偺儅僗僞乕僔僗僥儉偵側傝傑偡

丂

侽俢俠俫乣侽俢俥俫丗俽俲亅侾侾侽侽乮僆僾僔儑儞偺僉乕儃乕僪乯

丂俉俀俆俆傪巊梡偟偰偍傝丄侽俢俠俫乣侽俢俥俫偑巊梡斖埻

丂俬乛俷億乕僩偑僼儖僨乕僐乕僪偝傟偰偄側偄偺偱俰俷倄抂巕偲廳暋偟偰偄傑偡

丂偦偺堊捠忢俽俲亅侾侾侽侽傪傾僋僙僗偡傞応崌偼

丂杮懱撪偺俰俷倄抂巕傪嬛巭偡傞傛偆偵側偭偰偄傑偡丅

丂僉乕僙儗僋僩斣崋侽俈傪慖戰偟偨偲偒偵

丂僉乕儃乕僪偑巊梡嬛巭偵側傝俰俷倄抂巕傪巊梡偡傞傛偆偵側傝傑偡

丂

丂俵俙俼俲丂III扨懱偩偲億乕僩僨乕僞偺曐帩乮儔僢僠乯偼偝傟側偄偺偱

丂傑偢億乕僩侽俢俥俫乮俉俀俆俆俠倂乯偵侽俋俀俫傪彂偒偙傒擖弌椡偺愝掕偟偰偐傜

丂侽俢俤俫乮俉俀俆俆俹俠乯偵侽侽侽俫傪彂偒偙傫偱丄億乕僩侽俢俤俫傪撉傓

丂丂侽俥俥俫側傜俵俙俼俲丂III偺傒丄

丂丂侽侽侽俫側傜俵俙俼俲丂III亄俽俲亅侾侾侽侽偲側傝傑偡

丂

丂杮懱偺傒偩偲僨乕僞偼曐帩偝傟側偄偺偱侽侽侽俫傪彂偒崬傫偱傕侽俥俥俫偵側偭偰偟傑偄傑偡偑

丂俽俲亅侾侾侽侽愙懕偱偼俉俀俆俆偵傛偭偰侽侽侽俫偺彂偒崬傒偑惓忢偵峴傢傟傞偺傪棙梡偟偰敾抐偟傑偡

丂

侽俥侽俫乣侽俥俀俫:俥俵亅俈侽乮僆僾僔儑儞偺俥俵壒尮儐僯僢僩倄俵俀侾係俁傪巊梡乯

丂俰俷倄抂巕傗俽俲亅侾侾侽侽偲廳暋偟偰偄傑偡乮俽俲亅侾侾侽侽偲嫟梡晄壜乯

丂億乕僩侽俥侽俫丄侽俥侾俫偼俰俷倄抂巕偲廳側傞偺偱偡偑

丂俰俷倄抂巕偼擖椡偺傒偱俥俵儐僯僢僩偼婎杮弌椡偵側傝傑偡

丂侽俥俀俫偑擖椡偵側傞偺偱侽俢俠俫偲廳側傝傑偡偑俥俵儐僯僢僩偺夞楬偱俰俷倄抂巕偼巊梡嬛巭偵側傝傑偡

丂擔杮偺儅僗僞乕僔僗僥儉偱偼億乕僩侽俁俤俫偺倓俀傪侾偵偟偰俰俷倄抂巕傪嬛巭偵偟偰

丂愙懕僠僃僢僋傪峴偄傑偡乮俀庬椶偺愙懕僠僃僢僋偑昁梫乯

丂

俼俷俵僄儕傾偼僇乕僪丄僇乕僪儕僢僕偵傛偭偰梕検偑曄傝傑偡

侽俉侽侽侽俫偵偼俼俙俵傗俼俷俵傪嵹偣傞偙偲偑偱偒傑偡丅

杮懱撪偺俼俙俵偼俛俁抂巕傪侾偵偡傞帠偵傛偭偰巊梡嬛巭偵弌棃傑偡乮儅僗僞乕僔僗僥儉偼峏偵僜僼僩偱愗傝姺偊壜乯

儅僗僞乕僔僗僥儉偵偼俁偮偺僗儘僢僩乮僇乕僩儕僢僕丄僇乕僪丄奼挘抂巕乯偵傛偭偰儊儌儕傪嵹偣傞帠偑弌棃傑偡

僗儘僢僩偺愗傝姺偊偼億乕僩侽俁俤俫傪巊梡偟偰偄傑偡偑俵俙俼俲丂III偱偼億乕僩傪擿偄偰傕侽俥俥俫偵側傝傑偡

儅僗僞乕僔僗僥儉偱偼俬俹俴婲摦丄僗儘僢僩僠僃僢僋丄愗傝姺偊偱巊梡偟偨億乕僩侽俁俤俫偺撪梕偑

侽俠侽侽侽俫偵弌椡丄棙梡偟傑偡乮儅僗僞乕僔僗僥儉偺傒乯

丂

儊僈俼俷俵偼儊儌儕儅僢僷傪僇乕僩儕僢僕撪偵帩偪杮懱撪偵偼僶儞僋愗傝姺偊偺婡擻偼偁傝傑偣傫

傑偨婔偮偐偺儊儌儕儅僢僷偑偁傝傑偡偑惂屼偺曽朄偼偳偺僇乕僩儕僢僕傕傎傏摨偠偱

僶儞僋愗傝懼偊曽幃偱儊儌儕儅僢僾丒霓丒俬乛俷偵傛偭偰惂屼偝傟傑偡

傾僪儗僗偼侽俥俥俥俠俫乣侽俥俥俥俥俫傑偱巊梡偟偰偍傝丄侾俇俲俛偛偲愗傝懼傢傝傑偡

丂

俁俢傾僟僾僞偼侽俥俥俥俉俫乣侽俥俥俥俛俫偺斖埻偱

僜僼僩偱偼侽俥俥俥俛俫傪巊梡偟偰偄傑偡乮懠偺傾僪儗僗偼儈儔乕乯

僼儖僨僐乕僪偼偝傟偰偄側偄偺偱杮懱撪偺儚乕僋俼俙俵偺侽俢俥俥俠俫乣侽俢俥俥俥俫偼

巊梡弌棃傑偣傫乮儅僢僷偺儈儔乕偵側偭偰偄傑偡乯

丂

丂侽俥俥俥俉俫乣侽俥俥俥俛俫丗俁俢僔僗僥儉偱巊梡 捠忢侽俥俥俥俛俫偺傒巊梡乮倓侽偱嵍丄塃偺愗傝懼偊丠)

丂侽俥俥俥俠俫丂丂丂丂丂丂丂丗庡偵僶僢僋傾僢僾俼俙俵偺愗傝姺偊

丂侽俥俥俥俢俫丂丂丂丂丂丂丂丗杮懱偺侽侽侽侽侽俫乣侽俁俥俥俥俫偵僶儞僋傪慖戰

丂侽俥俥俥俤俫丂丂丂丂丂丂丂丗杮懱偺侽係侽侽侽俫乣侽俈俥俥俥俫偵僶儞僋傪慖戰

丂侽俥俥俥俥俫丂丂丂丂丂丂丂丗杮懱偺侽俉侽侽侽俫乣侽俛俥俥俥俫偵僶儞僋傪慖戰

丂

丂

俬乛俷億乕僩

丂

倁俢俹撪偱億乕僩惂屼傪峴偭偰偍傝

巊梡傾僪儗僗僶僗偼俙侾俆丆俙侾係丄俙俈丄俙俇丄俙侽偟偐宷偑偭偰偍傜偢

俙侾俆丄俙侾係偼乛俤倃俵侾丄俀梡偱丄俙俈丄俙俇丄俙侽偑億乕僩梡偵側傝傑偡

偟偨偑偭偰億乕僩偼侽係侽俫偛偲嬫愗傜傟傑偡

奼挘僐僱僋僞偵偼乛俲俛俽俤俴偲俙侽乣俙俀偑偁傞偺偱

億乕僩侽俠侽俫埲崀偺億乕僩偼壓埵係價僢僩偼侽乣俈傑偱惂屼偱偒傑偡丅

丂侽侽侽俫乣侽俁俥俫丗僐儞僩儘乕儖乮枹巊梡乯

丂侽係侽俫乣侽俈俥俫丗俹俽俧乛倁俢俹

丂侽俉侽俫乣侽俛俥俫丗倁俢俹

丂侽俠侽俫乣侽俥俥俫丗俰俷倄抂巕乛奼挘僐僱僋僞乮俥俵亅俈侽丄俽俲亅侾侾侽侽乯

丂

侽俁俤俫丗俵俙俼俲丂III偱偼枹巊梡

丂俵俙俼俲丂III偱偼僇乕僩儕僢僕偲僇乕僪偺暪梡丄杮懱撪俼俙俵偲奼挘俼俙俵乮侽俠侽侽侽俫埲崀乯偺巊梡傪

丂夞楬偱嬛巭傪寛傔偰偄傑偡偑儅僗僞乕僔僗僥儉埲崀偱偼偙偺億乕僩傪巊梡偟偰

丂僇乕僩儕僢僕傗杮懱撪俼俙俵偺愗傝姺偊摍傪峴偄傑偡

丂億乕僩侽俁俤俫偲億乕僩侽俁俥俫偑俵俙俼俲丂III偲儅僗僞乕僔僗僥儉偺戝偒側堘偄偵側傝

丂僴乕僪傛傝側偺偑俵俙俼俲丂III丄僜僼僩傛傝偱億乕僩侽俁俤俫偲億乕僩侽俁俥俫傪巊梡偡傞偺偑儅僗僞乕僔僗僥儉偲偄偊傑偡丅

丂俵俙俼俲丂III偱偼枹巊梡側偺偱僨乕僞曐帩偝傟偰偄側偄偺偱偡偑撉傓偨傃偵僨乕僞偑曄壔偟傑偡

丂儅僗僞乕僔僗僥儉偱偼巊梡偟偰偄傑偡偑彂偒崬傒梡億乕僩側偺偱撉傓偲侽俥俥俫偵側傝傑偡

丂偦偺堊偵儅僗僞乕僔僗僥儉婲摦偺僗儘僢僩僠僃僢僋偱億乕僩侽俁俤俫偑儚乕僋侽俠侽侽侽俫偺撪梕偵側傝

丂俥俵壒尮傪巊梡偡傞応崌偵偙偺侽俠侽侽侽俫傪撉傫偱億乕僩侽俁俤俫乮俰俷倄抂巕嬛巭乯偵偡傞帠偱

丂傾僋僙僗偡傞帠偵側傝傑偡

丂

侽俁俥俫丗俵俙俼俲丂III偱偼枹巊梡

丂丂丂丂丂儅僗僞乕僔僗僥儉偱偼儊儌儕丄俰俷倄抂巕乛俥俵儐僯僢僩偺惂屼傪峴偄傑偡

丂

侽俈俤俫丗尰嵼偺倁僇僂儞僞乕乮擖椡乯

侽俈俥俫丗尰嵼偺俫僇僂儞僞乕乮擖椡乯乛俹俽俧乮弌椡乯

丂

侽俛俤俫乣侽俛俥俫丗倁俢俹

丂

億乕僩侽俠侽俫乣侽俠侾俫丗俰俷倄抂巕乮儈儔乕乯

丂僨僐乕僪偝傟偰偄側偄偺偱億乕僩侽俢俠俫乣侽俢俢俫偺儈儔乕偵側傝傑偡乮奼挘抂巕偵壗傕宷偘側偄応崌乯

丂晄巚媍側偍忛僺僢僩億僢僩偱偼億乕僩侽俠侽俫乣侽俠侾俫傪巊梡偟偰偄傑偡

丂偨偩偟俥俵儐僯僢僩傪晅偗偰偄傞応崌偼摦嶌偑偍偐偟偔側偭偰偟傑偆偺偱巊梡偟側偄曽偑椙偄偱偡

丂

侽俢俠俫丗俰俷倄抂巕乮擖椡乯

丂倓俈丗俰俷倄俀丂俀僺儞乮俢俷倂俶丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俇丗俰俷倄俀丂侾僺儞乮倀俹丂丂丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俆丗俰俷倄侾丂俋僺儞乮俀儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓係丗俰俷倄侾丂俇僺儞乮侾儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俁丗俰俷倄侾丂係僺儞乮俼俬俧俫俿乯丂侾亖僆僼丄侽亖僆儞

丂倓俀丗俰俷倄侾丂俁僺儞乮俴俤俥俿丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侾丗俰俷倄侾丂俀僺儞乮俢俷倂俶丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侽丗俰俷倄侾丂侾僺儞乮倀俹丂丂丂乯丂侾亖僆僼丄侽亖僆儞

丂

侽俢俢俫丗俰俷倄抂巕亄俠俷俶抂巕乮擖椡乯

丂倓俈丗俬俠俋丂俈係俴俽俀俆俈偺13僺儞丂侾偱屌掕乮枹巊梡乯

丂倓俇丗俬俠俋丂俈係俴俽俀俆俈偺10僺儞丂侾偱屌掕乮枹巊梡乯

丂倓俆丗俬俠俋丂俈係俴俽俀俆俈偺俇僺儞丂侾偱屌掕乮枹巊梡乯

丂倓係丗俠俷俶抂巕丂丂丂丂丂丂丂丂丂丂丂侾亖僆僼丄侽亖僆儞

丂倓俁丗俰俷倄俀丂俋僺儞乮俀儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俀丗俰俷倄俀丂俇僺儞乮侾儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侾丗俰俷倄俀丂係僺儞乮俼俬俧俫俿乯丂侾亖僆僼丄侽亖僆儞

丂倓侽丗俰俷倄俀丂俁僺儞乮俴俤俥俿丂乯丂侾亖僆僼丄侽亖僆儞

丂

丂仏億乕僩侽俢俢俫傪傒偰擔杮偺僴乕僪偐奀奜偺僴乕僪偑敾抐弌棃傑偡

丂丂億乕僩侽俁俥俫偵侽俥俆俫傪弌椡偟偰億乕僩侽俢俢俫傪尒傞

丂丂億乕僩侽俁俥俫偵侽俆俆俫傪弌椡偟偰億乕僩侽俢俢俫傪尒傞帠偱敾抐弌棃傑偡丅

丂丂丂俵俙俼俲丂III偺応崌

丂丂丂丂億乕僩侽俁俥俫偼巊梡偟偰偄側偄偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈乣俇偼侾侾偱屌掕

丂

丂丂丂擔杮偺儅僗僞乕僔僗僥儉偺応崌

丂丂丂丂億乕僩侽俁俥俫偺倓俁乣侾偺撪梕偼侽側偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈乣俇偼俀夞偲傕侽侽

丂

丂丂丂奀奜偺儅僗僞乕僔僗僥儉偺応崌

丂丂丂丂俰俷倄抂巕偺俈僺儞偺愝掕偺抣偑擖傞偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈亅俇偼侾侾偲侽侽

丂

丂丂丂侾侾偐傜侾侾側傜俵俙俼俲丂III

丂丂丂侽侽偐傜侽侽側傜擔杮偺儅僗僞乕僔僗僥儉

丂丂丂侾侾偐傜侽侽偵曄壔偡傞側傜奀奜偺儅僗僞乕僔僗僥儉偵側傝傑偡

丂

侽俢俠俫乣侽俢俥俫丗俽俲亅侾侾侽侽乮僆僾僔儑儞偺僉乕儃乕僪乯

丂俉俀俆俆傪巊梡偟偰偍傝丄侽俢俠俫乣侽俢俥俫偑巊梡斖埻

丂俬乛俷億乕僩偑僼儖僨乕僐乕僪偝傟偰偄側偄偺偱俰俷倄抂巕偲廳暋偟偰偄傑偡

丂偦偺堊捠忢俽俲亅侾侾侽侽傪傾僋僙僗偡傞応崌偼

丂杮懱撪偺俰俷倄抂巕傪嬛巭偡傞傛偆偵側偭偰偄傑偡丅

丂僉乕僙儗僋僩斣崋侽俈傪慖戰偟偨偲偒偵

丂僉乕儃乕僪偑巊梡嬛巭偵側傝俰俷倄抂巕傪巊梡偡傞傛偆偵側傝傑偡

丂

丂俵俙俼俲丂III扨懱偩偲億乕僩僨乕僞偺曐帩乮儔僢僠乯偼偝傟側偄偺偱

丂傑偢億乕僩侽俢俥俫乮俉俀俆俆俠倂乯偵侽俋俀俫傪彂偒偙傒擖弌椡偺愝掕偟偰偐傜

丂侽俢俤俫乮俉俀俆俆俹俠乯偵侽侽侽俫傪彂偒偙傫偱丄億乕僩侽俢俤俫傪撉傓

丂丂侽俥俥俫側傜俵俙俼俲丂III偺傒丄

丂丂侽侽侽俫側傜俵俙俼俲丂III亄俽俲亅侾侾侽侽偲側傝傑偡

丂

丂杮懱偺傒偩偲僨乕僞偼曐帩偝傟側偄偺偱侽侽侽俫傪彂偒崬傫偱傕侽俥俥俫偵側偭偰偟傑偄傑偡偑

丂俽俲亅侾侾侽侽愙懕偱偼俉俀俆俆偵傛偭偰侽侽侽俫偺彂偒崬傒偑惓忢偵峴傢傟傞偺傪棙梡偟偰敾抐偟傑偡

丂

侽俥侽俫乣侽俥俀俫:俥俵亅俈侽乮僆僾僔儑儞偺俥俵壒尮儐僯僢僩倄俵俀侾係俁傪巊梡乯

丂俰俷倄抂巕傗俽俲亅侾侾侽侽偲廳暋偟偰偄傑偡乮俽俲亅侾侾侽侽偲嫟梡晄壜乯

丂億乕僩侽俥侽俫丄侽俥侾俫偼俰俷倄抂巕偲廳側傞偺偱偡偑

丂俰俷倄抂巕偼擖椡偺傒偱俥俵儐僯僢僩偼婎杮弌椡偵側傝傑偡

丂侽俥俀俫偑擖椡偵側傞偺偱侽俢俠俫偲廳側傝傑偡偑俥俵儐僯僢僩偺夞楬偱俰俷倄抂巕偼巊梡嬛巭偵側傝傑偡

丂擔杮偺儅僗僞乕僔僗僥儉偱偼億乕僩侽俁俤俫偺倓俀傪侾偵偟偰俰俷倄抂巕傪嬛巭偵偟偰

丂愙懕僠僃僢僋傪峴偄傑偡乮俀庬椶偺愙懕僠僃僢僋偑昁梫乯

丂

婡庬偺敾抐

丂

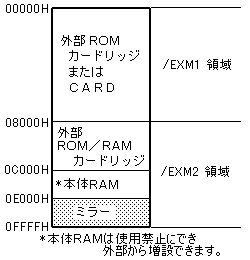

俵俙俼俲III偲慜偺婡庬乮偄傢備傞慡婡庬乯偲偺敾抐曽朄偼儊儌儕偺儈儔乕偺堘偄傪棙梡偟偰敾抐偟傑偡

丂俽俧亅侾侽侽侽丂丂侾俲俛儌僨儖丂侽俠侽侽侽俫乣侽俠俁俥俥俫乮埲崀偼儈儔乕乯

丂俽俠亅俁侽侽侽摍丂俀俲俛儌僨儖丂侽俠侽侽侽俫乣侽俠俈俥俥俫乮埲崀偼儈儔乕乯

丂俵俙俼俲 III摍丂丂俉俲俛儌僨儖丂侽俠侽侽侽俫乣侽俢俥俥俥俫乮埲崀偼儈儔乕乯

丂

侽俠侽侽侽俫偲侽俢侽侽侽俫偺椉曽偵侽侽侽俫傪彂偒崬傫偱偍偒傑偡

侽俠侽侽侽俫偵僨乕僞乮椺偊偽侽俆俆俫乯傪彂偒崬傒侽俢侽侽侽俫偺僨乕僞傪撉傒傑偡

慡婡庬丄儅儖僠價僕儑儞偩偲儈儔乕偵側偭偰偄傞偺偱侽俠侽侽侽俫偲侽俢侽侽侽俫偼摨偠抣偵側傝傑偡

俵俙俼俲丂III埲崀偩偲堘偆僨乕僞偵側傝傑偡

丂

丂

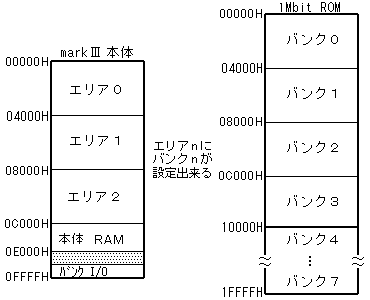

儊儌儕儅僢僷丂俁侾俆亅俆俀侽俉

丂

堦斣屆偄儊儌儕儅僢僷偱偡偑丄偙偺儅僢僷偑婎弨偲側傝傑偡

儅僢僷撪憼俼俷俵偺巊梡婎斅俿倄俹俤亅俶傕摨條偺傾僋僙僗偵側傝傑偡

巊梡億乕僩偼儊儌儕儅僢僾丒僪丒俬乛俷傪嵦梡偟偰

斖埻偼侽俥俥俥俢俫乣侽俥俥俥俥俫偵側傝僶儞僋偼侽乣俈傑偱偱偡乮嵟戝侾俵俛倝倲乯

拲堄偡傞偺偼杮懱撪憼俼俙俵偼侽俠侽侽侽俫乣侽俢俥俥俥俫側偺偱偡偑

侽俤侽侽侽俫亅侽俥俥俥俥俫偑儈儔乕偵側偭偰偄傑偡

偦偺堊僗僞僢僋億僀儞僞偺巜掕傪侽俢俥俥俥俫偵偡傞偲侽俢俥俥俥俫偐傜僗僞僢僋偺僨乕僞偑

擖傞偺偲摨帪偵侽俥俥俥俥俫偺儅僢僷偵傕僨乕僞偑擖傞堊丄岆摦嶌傪婲偙偟傑偡

偦偙偱僗僞僢僋億僀儞僞偺巜掕偼侽俢俥俥侽俫曈傝偵巜掕偟偰岆摦嶌傪杊偖昁梫偑偁傝傑偡

峏偵儅僗僞乕僔僗僥儉偱偼侽俈俥俥侽俫亅侽俈俥俥俥俫偺儔僀僩傕嬛巭偵側傝傑偡

丂

丂侽俥俥俥俢俫丗僄儕傾侽乮侽侽侽侽侽俫乣侽俁俥俥俥俫乯偺僶儞僋巜掕

丂丂倓俈丗侽

丂丂倓俇丗侽

丂丂倓俆丗侽

丂丂倓係丗侽

丂丂倓俁丗侽

丂丂倓俀丗僶儞僋丂俢俀

丂丂倓侾丗僶儞僋丂俢侾

丂丂倓侽丗僶儞僋丂俢侽

丂

丂侽俥俥俥俤俫丗僄儕傾侾乮侽係侽侽侽俫乣侽俈俥俥俥俫乯偺僶儞僋巜掕

丂丂倓俈丗侽

丂丂倓俇丗侽

丂丂倓俆丗侽

丂丂倓係丗侽

丂丂倓俁丗侽

丂丂倓俀丗僶儞僋丂俢俀

丂丂倓侾丗僶儞僋丂俢侾

丂丂倓侽丗僶儞僋丂俢侽

丂侽俥俥俥俥俫丗僄儕傾俀乮侽俉侽侽侽俫乣侽俛俥俥俥俫乯偺僶儞僋巜掕

丂丂倓俈丗侽

丂丂倓俇丗侽

丂丂倓俆丗侽

丂丂倓係丗侽

丂丂倓俁丗侽

丂丂倓俀丗僶儞僋丂俢俀

丂丂倓侾丗僶儞僋丂俢侾

丂丂倓侽丗僶儞僋丂俢侽

丂

丂

侾俵倐倝倲僇乕僩儕僢僕丂171-5363乮俿倄俹俤亅俥乯偺夞楬恾

丂

侾俵倐倝倲僇乕僩儕僢僕丂171-5363乮俿倄俹俤亅俥乯偺夞楬恾

丂

丂

儊儌儕儅僢僷丂俁侾俆亅俆俀俁俆

丂

俁侾俆亅俆俀侽俉傪奼挘偟偰僶僢僋傾僢僾俼俙俵丄僶儞僋悢傪奼挘偟偨儅僢僷偵側傝傑偡丅

弌椡億乕僩偼儊儌儕儅僢僾丒僪丒俬乛俷傪嵦梡偟偰

巊梡斖埻偼侽俥俥俥俠俫乣侽俥俥俥俥俫偵側傝僶儞僋偼侽乣俁侾傑偱偱偡乮嵟戝係俵俛倝倲丠乯

僶僢僋傾僢僾俼俙俵偵傕惂屼偑弌棃傑偡

媽儅僢僷乮俁侾俆亅俆俀侽俉乯摨條偵僗僞僢僋億僀儞僞偺巜掕偵拲堄偟偰壓偝偄丅

丂

侽俥俥俥俠俫丗儊儌儕僐儞僩儘乕儖

丂倓俈丗儔僀僩僾儘僥僋僩乮奐敪梡乯丂丂丂丂丂丂丂丂丂丂侾亖儕乕僪乛儔僀僩丄侽亖儕乕僪偺傒

丂倓俇丗侽

丂倓俆丗侽

丂倓係丗僄儕傾係乮侽俠侽侽侽俫乣侽俢俥俥俥俫乯偺慖戰丂侾亖奜晹俼俙俵値値丄侽亖杮懱俼俙俵

丂倓俁丗僄儕傾俀乮侽俉侽侽侽俫乣侽俛俥俥俥俫乯偺慖戰丂侾亖奜晹俼俙俵値値丄侽亖俼俷俵

丂倓俀丗奜晹俼俙俵偺僶儞僋丂丂丂丂丂丂丂丂丂丂丂丂丂丂侾亖奜晹俼俙俵侽俀丄侽亖奜晹俼俙俵侽侾

丂倓侾丗僶儞僋丂僔僼僩丂乮捠忢偼侽乯

丂倓侽丗僶儞僋丂僔僼僩丂乮捠忢偼侽乯

丂

丂丂仏僶儞僋僔僼僩偼儊僈俼俷俵帺懱偺憤梕検傪侾俇俲偛偲偵嬫愗偭偨僶儞僋俶倧丏偺巜掕傪偢傜偟傑偡丅

丂丂丂僶儞僋僔僼僩侽侽丂侽侽侽俫丆侽侽侾俫丆侽侽俀俫丏丏丏

丂丂丂僶儞僋僔僼僩侽侾丂侽侾俉俫丆侽侾俋俫丆侽侾俙俫丏丏丏

丂丂丂僶儞僋僔僼僩侾侽丂侽侾侽俫丆侽侾侾俫丆侽侾俀俫丏丏丏

丂丂丂僶儞僋僔僼僩侾侾丂侽侽俉俫丆侽侽俋俫丆侽侽俙俫丏丏丏

丂丂丂丂僶儞僋俶倧丏偼侽侽侽俫乣侽侾俥俫偱僶儞僋僔僼僩偱偢傟偨応崌偼侾俥俫偺師偼侽侽侽俫偵側傝傑偡丅

丂

丂丂奜晹俼俙俵乮僶僢僋傾僢僾俼俙俵乯偼嵟戝俁俀俲俛傑偱搵嵹壜

丂丂偙傟傪俀偮偺僶儞僋偵偟偰愗傝懼傢傞帠偑壜擻丠乮枹妋擣乯

丂

侽俥俥俥俢俫丗僄儕傾侽乮侽侽侽侽侽俫乣侽俁俥俥俥俫乯偺僶儞僋巜掕

丂倓俈丗侽

丂倓俇丗侽

丂倓俆丗侽

丂倓係丗僶儞僋丂俢係

丂倓俁丗僶儞僋丂俢俁

丂倓俀丗僶儞僋丂俢俀

丂倓侾丗僶儞僋丂俢侾

丂倓侽丗僶儞僋丂俢侽

乮拲乯僄儕傾侽偺侽侽侽侽侽俫乣侽俁俥俥俥俫偼僶儞僋仈侽侽丗侽侽侽侽侽俫乣侽俁俥俥俥俫屌掕偵側傝

丂丂丂偳偺僶儞僋傪巜掕偟偰傕侽侽侽侽侽俫乣侽俁俥俥俥俫偼曄壔偟傑偣傫

丂丂丂僶儞僋僔僼僩偑侽侽埲奜偺帪偼晄柧偱偡丅

丂

侽俥俥俥俤俫丗僄儕傾侾乮侽係侽侽侽俫乣侽俈俥俥俥俫乯偺僶儞僋巜掕

丂倓俈丗侽

丂倓俇丗侽

丂倓俆丗侽

丂倓係丗僶儞僋丂俢係

丂倓俁丗僶儞僋丂俢俁

丂倓俀丗僶儞僋丂俢俀

丂倓侾丗僶儞僋丂俢侾

丂倓侽丗僶儞僋丂俢侽

丂

侽俥俥俥俥俫丗僄儕傾俀乮侽俉侽侽侽俫乣侽俛俥俥俥俫乯偺僶儞僋巜掕

丂倓俈丗侽

丂倓俇丗侽

丂倓俆丗侽

丂倓係丗僶儞僋丂俢係

丂倓俁丗僶儞僋丂俢俁

丂倓俀丗僶儞僋丂俢俀

丂倓侾丗僶儞僋丂俢侾

丂倓侽丗僶儞僋丂俢侽

丂

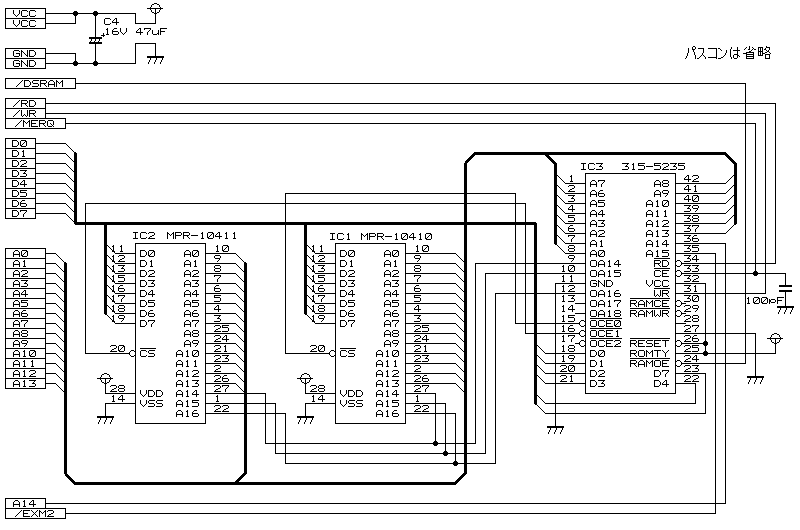

俀俵倐倝倲僇乕僩儕僢僕丂僗儁乕僗僴儕傾乕丂侾俈侾亅俆係俁俋乮侾俵仏俀僶乕僕儑儞乯偺夞楬恾

僗儁乕僗僴儕傾乕傗傾僂僩儔儞偱巊梡偝傟偰偄傑偡丅

偝傜偵戝梕検偺俼俷俵傕僒億乕僩偱偒傞傛偆偵側傝丄儅僢僷乕偺傾僋僙僗傕彮偟奼挘偝傟偰偄傑偡丅

偨偩偟丄婎杮揑側傾僋僙僗曽朄偼摨偠偱丄奀奜偺儅僗僞乕僔僗僥儉偺俼俷俵僠僃僢僋偺搒崌偱

摨偠曽朄偱側偄偲僠僃僢僋偱偒側偄堊偩偲巚傢傟傑偡丅

丂

俀俵倐倝倲僇乕僩儕僢僕丂僗儁乕僗僴儕傾乕丂侾俈侾亅俆係係侽乮俀俵仏侾僶乕僕儑儞乯偺夞楬恾

僗儁乕僗僴儕傾乕傗傾僂僩儔儞偱巊梡偝傟偰偄傑偡丅

偝傜偵戝梕検偺俼俷俵傕僒億乕僩偱偒傞傛偆偵側傝丄儅僢僷乕偺傾僋僙僗傕彮偟奼挘偝傟偰偄傑偡丅

偨偩偟丄婎杮揑側傾僋僙僗曽朄偼摨偠偱丄奀奜偺儅僗僞乕僔僗僥儉偺俼俷俵僠僃僢僋偺搒崌偱

摨偠曽朄偱側偄偲僠僃僢僋偱偒側偄堊偩偲巚傢傟傑偡丅

丂

俀俵倐倝倲僇乕僩儕僢僕丂僗儁乕僗僴儕傾乕丂侾俈侾亅俆係係侽乮俀俵仏侾僶乕僕儑儞乯偺夞楬恾

摨偠偔僗儁乕僗僴儕傾乕偺俀俵俛倝倲俼俷俵仏侾僶乕僕儑儞偱偡丅乮屻婜僶乕僕儑儞丠乯

摨偠儊儌儕儅僢僷乕傪巊梡偟偰偄傞傛偆側偺偱偡偑丄庒姳攝慄偑堘偭偰偄傑偡

偙偙偱堘偆売強偼儅僢僷乕偺俁侾俆亅俆俁俀俆偺俀俆僺儞偺擖椡偲乛俠俤侽丄乛俠俤侾偺弌椡晹暘偱偡

巆傝偺嬻敀晹暘偼嫲傜偔丄僶儞僋愗傝姺偊偺乛俠俤偲丄偦偺弌椡偺僞僀僾偺慖戰偵巊傢傟傞偲巚傢傟傑偡

俼俷俵偺柤徧俵俹俼亅侾侽係侾偑僗儁乕僗僴儕乕傾傪巜偟偰丄巆傝偺侾働僞偑俼俷俵偺庬椶丠

儅僢僷乕偵宷偑傞僨乕僞僶僗偼倓俈偲倓係乣侽側偺偱倓俈偑俼俙俵偺僀僱乕僽儖丄

倓係乣侽偑僶儞僋値値乮侽侽侽俫乣侽侾俥俫乯偵側傞偲巚傢傟傑偡

傑偨丄搵嵹壜擻偺儊儌儕偼侾俵俛倝倲丄俀俵俛倝倲丄係俵俛倝倲偱嵟戝儊儌儕偼係俵俛倝倲偺傛偆偱偡丅

丂

丂

俀俵倐倝倲僇乕僩儕僢僕丂擬媴峛巕墍丂侾俈侾亅俆係係侾乮俀俵俼俷俵丂俁俀僺儞僶乕僕儑儞乯偺夞楬恾

摨偠偔僗儁乕僗僴儕傾乕偺俀俵俛倝倲俼俷俵仏侾僶乕僕儑儞偱偡丅乮屻婜僶乕僕儑儞丠乯

摨偠儊儌儕儅僢僷乕傪巊梡偟偰偄傞傛偆側偺偱偡偑丄庒姳攝慄偑堘偭偰偄傑偡

偙偙偱堘偆売強偼儅僢僷乕偺俁侾俆亅俆俁俀俆偺俀俆僺儞偺擖椡偲乛俠俤侽丄乛俠俤侾偺弌椡晹暘偱偡

巆傝偺嬻敀晹暘偼嫲傜偔丄僶儞僋愗傝姺偊偺乛俠俤偲丄偦偺弌椡偺僞僀僾偺慖戰偵巊傢傟傞偲巚傢傟傑偡

俼俷俵偺柤徧俵俹俼亅侾侽係侾偑僗儁乕僗僴儕乕傾傪巜偟偰丄巆傝偺侾働僞偑俼俷俵偺庬椶丠

儅僢僷乕偵宷偑傞僨乕僞僶僗偼倓俈偲倓係乣侽側偺偱倓俈偑俼俙俵偺僀僱乕僽儖丄

倓係乣侽偑僶儞僋値値乮侽侽侽俫乣侽侾俥俫乯偵側傞偲巚傢傟傑偡

傑偨丄搵嵹壜擻偺儊儌儕偼侾俵俛倝倲丄俀俵俛倝倲丄係俵俛倝倲偱嵟戝儊儌儕偼係俵俛倝倲偺傛偆偱偡丅

丂

丂

俀俵倐倝倲僇乕僩儕僢僕丂擬媴峛巕墍丂侾俈侾亅俆係係侾乮俀俵俼俷俵丂俁俀僺儞僶乕僕儑儞乯偺夞楬恾

丂32僺儞偺儅僗僋俼俷俵傪巊梡偟偰偄傑偡丅

丂

係俵倐倝倲僇乕僩儕僢僕丂傾僼僞乕僶乕僫乕丂侾俈侾亅俆俆俉俋俢乮俀俵仏俀乯偺夞楬恾

丂32僺儞偺儅僗僋俼俷俵傪巊梡偟偰偄傑偡丅

丂

係俵倐倝倲僇乕僩儕僢僕丂傾僼僞乕僶乕僫乕丂侾俈侾亅俆俆俉俋俢乮俀俵仏俀乯偺夞楬恾

丂

係俵倐倝倲僇乕僩儕僢僕丂僼傽儞僞僔乕僗僞乕丂侾俈侾亅俆俆俉俁乮係俵亄俇係俲俛倝倲俽亅俼俙俵乯偺夞楬恾

丂

丂

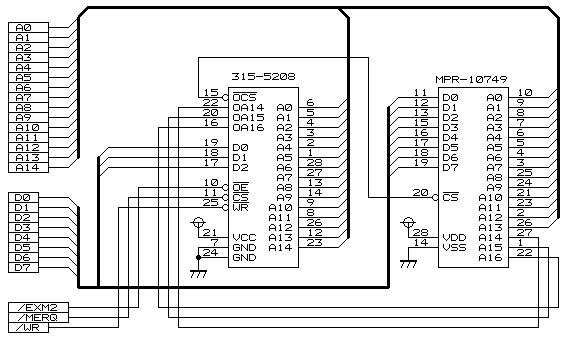

僇乕僩儕僢僕撪偺婎斅偺庬椶

侾俈侾亅俆俁俇俀丂丂丂丗俿倄俹俤亅俶丂儅僢僷乕撪憼侾俵俛倝倲丂俼俷俵

侾俈侾亅俆俁俇俁亅侽侾丗俿倄俹俤亅俥丂俁侾俆亅俆俀侽俉亄侾俵俛倝倲丂俼俷俵

侾俈侾亅俆係俁俋丂丂丂丗俁侾俆亅俆俀俁俆亄侾俵俛倝倲丂俼俷俵仏俀

侾俈侾亅俆係係侽丂丂丂丗俁侾俆亅俆俀俁俆亄俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆侽侽丂丂丂丗俁侾俆亅俆俀俁俆亄侾俵俛倝倲丂俼俷俵亄俇係俲俽俼俙俵亄俵俛俁俈俈侾

侾俈侾亅俆俆侽俇丂丂丂丗儅僢僷乕撪憼俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆侾俉丂丂丂丗儅僢僷乕撪憼侾俵俛倝倲丂俼俷俵

侾俈侾亅俆侾俈俈丂丂丂丗俽俧亅侾侽侽侽梡偺婎斅傪僕儍儞僷乕慄傪巊偄俿倄俹俤亅俶偲摨條偵偟偨傕偺

侾俈侾亅俆俆俇係丂丂丂丗儅僢僷乕撪憼俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆俉俋俢丂丂丗俁侾俆亅俆俀俁俆亄俀俵俛倝倲丂俼俷俵仏俀

侾俈侾亅俆俆俉俁丂丂丂丗俁侾俆亅俆俀俁俆亄係俵俛倝倲丂俼俷俵亄俇係俲俽俼俙俵亄俿俆俀俋俥

丂

丂

係俵倐倝倲僇乕僩儕僢僕丂僼傽儞僞僔乕僗僞乕丂侾俈侾亅俆俆俉俁乮係俵亄俇係俲俛倝倲俽亅俼俙俵乯偺夞楬恾

丂

丂

僇乕僩儕僢僕撪偺婎斅偺庬椶

侾俈侾亅俆俁俇俀丂丂丂丗俿倄俹俤亅俶丂儅僢僷乕撪憼侾俵俛倝倲丂俼俷俵

侾俈侾亅俆俁俇俁亅侽侾丗俿倄俹俤亅俥丂俁侾俆亅俆俀侽俉亄侾俵俛倝倲丂俼俷俵

侾俈侾亅俆係俁俋丂丂丂丗俁侾俆亅俆俀俁俆亄侾俵俛倝倲丂俼俷俵仏俀

侾俈侾亅俆係係侽丂丂丂丗俁侾俆亅俆俀俁俆亄俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆侽侽丂丂丂丗俁侾俆亅俆俀俁俆亄侾俵俛倝倲丂俼俷俵亄俇係俲俽俼俙俵亄俵俛俁俈俈侾

侾俈侾亅俆俆侽俇丂丂丂丗儅僢僷乕撪憼俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆侾俉丂丂丂丗儅僢僷乕撪憼侾俵俛倝倲丂俼俷俵

侾俈侾亅俆侾俈俈丂丂丂丗俽俧亅侾侽侽侽梡偺婎斅傪僕儍儞僷乕慄傪巊偄俿倄俹俤亅俶偲摨條偵偟偨傕偺

侾俈侾亅俆俆俇係丂丂丂丗儅僢僷乕撪憼俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆俉俋俢丂丂丗俁侾俆亅俆俀俁俆亄俀俵俛倝倲丂俼俷俵仏俀

侾俈侾亅俆俆俉俁丂丂丂丗俁侾俆亅俆俀俁俆亄係俵俛倝倲丂俼俷俵亄俇係俲俽俼俙俵亄俿俆俀俋俥

丂

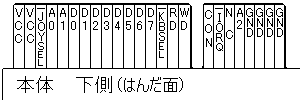

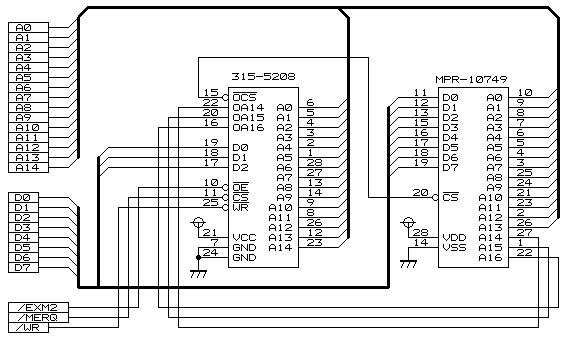

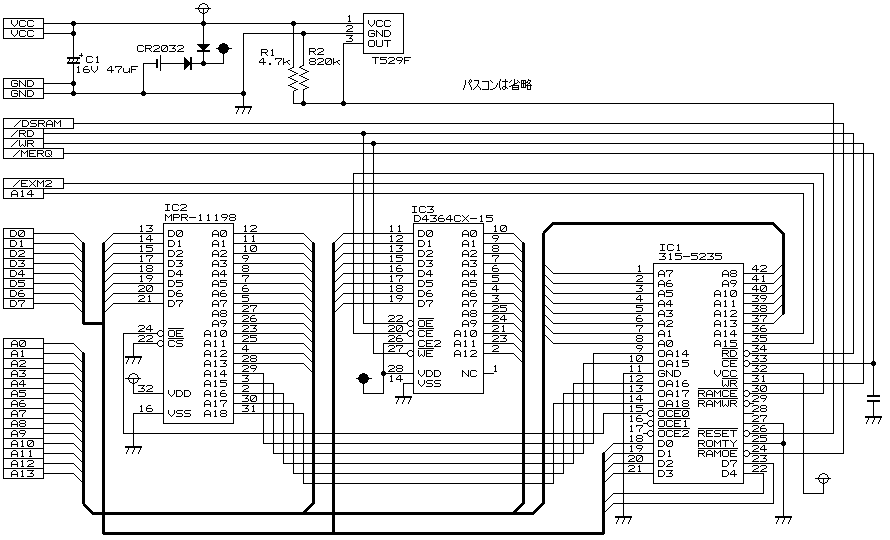

倁俢俹廃傝偺夞楬恾

丂

倁亅俼俙俵廃傝偺夞楬恾

丂

倁亅俼俙俵廃傝偺夞楬恾

丂

丂

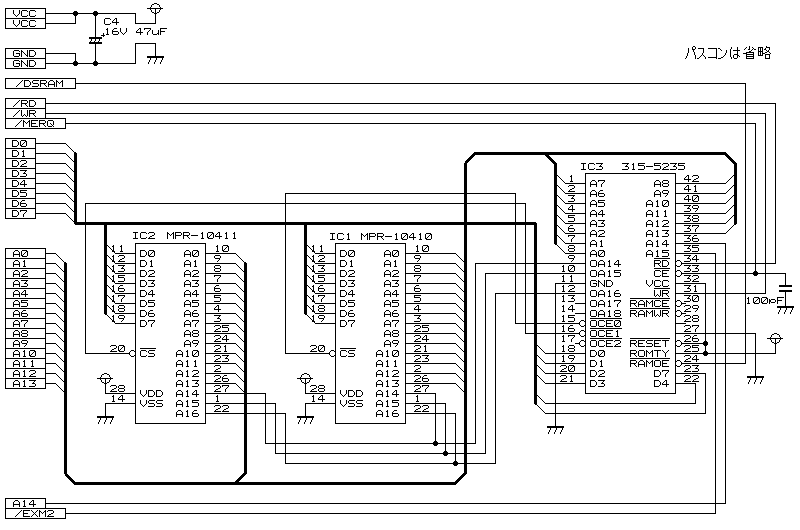

俰俷倄抂巕廃傝偺夞楬恾

丂

丂

俰俷倄抂巕廃傝偺夞楬恾

丂

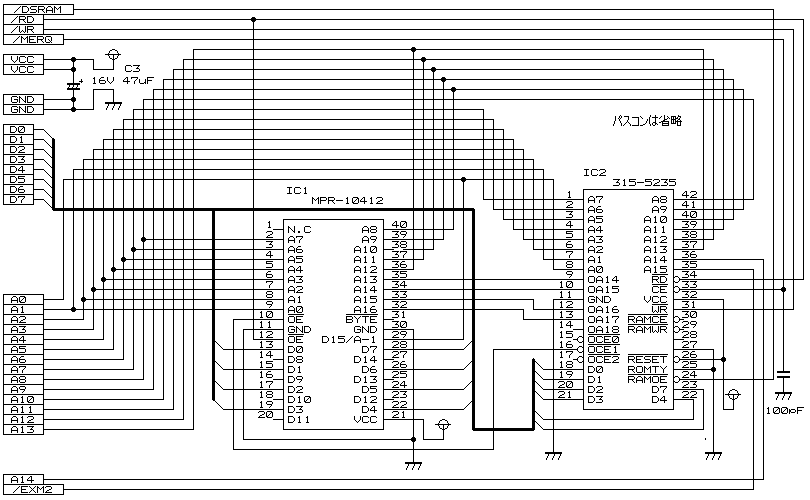

楢幩儐僯僢僩乮俼俥亅侾俆侽乯偺夞楬恾

丂

楢幩儐僯僢僩乮俼俥亅侾俆侽乯偺夞楬恾

俁俢傾僟僾僞偺夞楬恾

僒儞僾儖丂僟僂儞儘乕僪

僾儘僌儔儉偼慡偰僼儕乕偱丄僜乕僗偼"The Macroassembler AS"偱嶌惉偱偒傑偡丅

偦偟偰偁偔傑偱嶲峫偱偡丅

丂僌儗乕僩傾僀僗儂僢働乕梡僗億乕僣僷僢僪偺儊僀儞夞楬恾

丂俛俧丂俿俤俽俿僾儘僌儔儉丂乮俵俙俼俲III丄儅僗僞乕僔僗僥儉丄僄儈儏儗乕僞偱偺摦嶌壜乯

丂俬乛俷億乕僩丂俹倕倕倫倝値倗僾儘僌儔儉丂乮俵俙俼俲III丄儅僗僞乕僔僗僥儉丄僄儈儏儗乕僞偱偺摦嶌壜乯

丂倁俢俹丂俼仈侽俁丂僥僗僩僾儘僌儔儉丂乮俵俙俼俲III丄儅僗僞乕僔僗僥儉偱偺摦嶌壜丄僄儈儏儗乕僞偱偺摦嶌晄壜乯

丂

Home 傊栠傞

俙侽乣俙侾係丗傾僪儗僗丂僶僗

俢侽乣俢俈 丗僨乕僞丂丂僶僗

乛俠俙俼俢丂丗俠俙俼俢僗儘僢僩偺巊梡丂侾亖巊梡晄壜丄侽亖巊梡壜

乛俢俽俼俙俵丗杮懱撪偺俼俙俵偺巊梡丂丂侾亖巊梡晄壜丄侽亖巊梡壜

乛俤倃俵侾丂丗侽俉侽侽侽俫偺俠俽乮晧椣棟乯

乛俤倃俵俀丂丗侽侽侽侽侽俫偺俠俽乮晧椣棟乯

俠俷俶丂丂丂丗奼挘僐僱僋僞偺18僺儞偲捈寢

丂

俛俀乮乛俠俙俼俢乯偼捠忢偺僎乕儉偺偲偒偼

倁俠俠偲僔儑乕僩偝傟偰偄偰俁俢僌儔僗巊梡壜擻僜僼僩偱俶丏俠丏偲側偭偰偄傑偡

偦偺堊俁俢僌儔僗懳墳偺僎乕儉偲僇乕僪偺僎乕儉傪巋偟側偑傜偩偲

僶僗嫞憟偡傞嫲傟偑偁傝傑偡

乛俠俙俼俢偼俵俙俼俲 III愱梡偺抂巕偱偡乮婡庬偛偲偵堘偄偑偁傝傑偡乯

丂

丂

奼挘抂巕恾

俙侽乣俙侾係丗傾僪儗僗丂僶僗

俢侽乣俢俈 丗僨乕僞丂丂僶僗

乛俠俙俼俢丂丗俠俙俼俢僗儘僢僩偺巊梡丂侾亖巊梡晄壜丄侽亖巊梡壜

乛俢俽俼俙俵丗杮懱撪偺俼俙俵偺巊梡丂丂侾亖巊梡晄壜丄侽亖巊梡壜

乛俤倃俵侾丂丗侽俉侽侽侽俫偺俠俽乮晧椣棟乯

乛俤倃俵俀丂丗侽侽侽侽侽俫偺俠俽乮晧椣棟乯

俠俷俶丂丂丂丗奼挘僐僱僋僞偺18僺儞偲捈寢

丂

俛俀乮乛俠俙俼俢乯偼捠忢偺僎乕儉偺偲偒偼

倁俠俠偲僔儑乕僩偝傟偰偄偰俁俢僌儔僗巊梡壜擻僜僼僩偱俶丏俠丏偲側偭偰偄傑偡

偦偺堊俁俢僌儔僗懳墳偺僎乕儉偲僇乕僪偺僎乕儉傪巋偟側偑傜偩偲

僶僗嫞憟偡傞嫲傟偑偁傝傑偡

乛俠俙俼俢偼俵俙俼俲 III愱梡偺抂巕偱偡乮婡庬偛偲偵堘偄偑偁傝傑偡乯

丂

丂

奼挘抂巕恾

俥俵壒尮儐僯僢僩傗僉乕儃乕僪俽俲亅侾侾侽侽偺愙懕抂巕偱偡

乛俰俷倄俽俤俴偼僕儑僀僗僥傿僋廃傝偲楢摦偟偰偍傝

乛俰俷倄俽俤俴丄乛俲俛俽俤俴丄乛俼俢偺俁偮偑侽側傜俰俷倄抂巕偑巊梡壜擻偵側傝傑偡

俛侾侾偼俽俲亅侾侾侽侽偩偲俹俛係丄杮懱偩偲僇僙僢僩抂巕偺俛侾侾偵宷偑偭偰偍傝

億乕僩偺侽俢俢俫偺倓係偱忬懺偑擿偔偙偲偑弌棃傑偡丅

丂

丂

儊儌儕丂儅僢僾

俥俵壒尮儐僯僢僩傗僉乕儃乕僪俽俲亅侾侾侽侽偺愙懕抂巕偱偡

乛俰俷倄俽俤俴偼僕儑僀僗僥傿僋廃傝偲楢摦偟偰偍傝

乛俰俷倄俽俤俴丄乛俲俛俽俤俴丄乛俼俢偺俁偮偑侽側傜俰俷倄抂巕偑巊梡壜擻偵側傝傑偡

俛侾侾偼俽俲亅侾侾侽侽偩偲俹俛係丄杮懱偩偲僇僙僢僩抂巕偺俛侾侾偵宷偑偭偰偍傝

億乕僩偺侽俢俢俫偺倓係偱忬懺偑擿偔偙偲偑弌棃傑偡丅

丂

丂

儊儌儕丂儅僢僾

俼俷俵僄儕傾偼僇乕僪丄僇乕僪儕僢僕偵傛偭偰梕検偑曄傝傑偡

侽俉侽侽侽俫偵偼俼俙俵傗俼俷俵傪嵹偣傞偙偲偑偱偒傑偡丅

杮懱撪偺俼俙俵偼俛俁抂巕傪侾偵偡傞帠偵傛偭偰巊梡嬛巭偵弌棃傑偡乮儅僗僞乕僔僗僥儉偼峏偵僜僼僩偱愗傝姺偊壜乯

儅僗僞乕僔僗僥儉偵偼俁偮偺僗儘僢僩乮僇乕僩儕僢僕丄僇乕僪丄奼挘抂巕乯偵傛偭偰儊儌儕傪嵹偣傞帠偑弌棃傑偡

僗儘僢僩偺愗傝姺偊偼億乕僩侽俁俤俫傪巊梡偟偰偄傑偡偑俵俙俼俲丂III偱偼億乕僩傪擿偄偰傕侽俥俥俫偵側傝傑偡

儅僗僞乕僔僗僥儉偱偼俬俹俴婲摦丄僗儘僢僩僠僃僢僋丄愗傝姺偊偱巊梡偟偨億乕僩侽俁俤俫偺撪梕偑

侽俠侽侽侽俫偵弌椡丄棙梡偟傑偡乮儅僗僞乕僔僗僥儉偺傒乯

丂

儊僈俼俷俵偼儊儌儕儅僢僷傪僇乕僩儕僢僕撪偵帩偪杮懱撪偵偼僶儞僋愗傝姺偊偺婡擻偼偁傝傑偣傫

傑偨婔偮偐偺儊儌儕儅僢僷偑偁傝傑偡偑惂屼偺曽朄偼偳偺僇乕僩儕僢僕傕傎傏摨偠偱

僶儞僋愗傝懼偊曽幃偱儊儌儕儅僢僾丒霓丒俬乛俷偵傛偭偰惂屼偝傟傑偡

傾僪儗僗偼侽俥俥俥俠俫乣侽俥俥俥俥俫傑偱巊梡偟偰偍傝丄侾俇俲俛偛偲愗傝懼傢傝傑偡

丂

俁俢傾僟僾僞偼侽俥俥俥俉俫乣侽俥俥俥俛俫偺斖埻偱

僜僼僩偱偼侽俥俥俥俛俫傪巊梡偟偰偄傑偡乮懠偺傾僪儗僗偼儈儔乕乯

僼儖僨僐乕僪偼偝傟偰偄側偄偺偱杮懱撪偺儚乕僋俼俙俵偺侽俢俥俥俠俫乣侽俢俥俥俥俫偼

巊梡弌棃傑偣傫乮儅僢僷偺儈儔乕偵側偭偰偄傑偡乯

丂

丂侽俥俥俥俉俫乣侽俥俥俥俛俫丗俁俢僔僗僥儉偱巊梡 捠忢侽俥俥俥俛俫偺傒巊梡乮倓侽偱嵍丄塃偺愗傝懼偊丠)

丂侽俥俥俥俠俫丂丂丂丂丂丂丂丗庡偵僶僢僋傾僢僾俼俙俵偺愗傝姺偊

丂侽俥俥俥俢俫丂丂丂丂丂丂丂丗杮懱偺侽侽侽侽侽俫乣侽俁俥俥俥俫偵僶儞僋傪慖戰

丂侽俥俥俥俤俫丂丂丂丂丂丂丂丗杮懱偺侽係侽侽侽俫乣侽俈俥俥俥俫偵僶儞僋傪慖戰

丂侽俥俥俥俥俫丂丂丂丂丂丂丂丗杮懱偺侽俉侽侽侽俫乣侽俛俥俥俥俫偵僶儞僋傪慖戰

丂

丂

俬乛俷億乕僩

丂

倁俢俹撪偱億乕僩惂屼傪峴偭偰偍傝

巊梡傾僪儗僗僶僗偼俙侾俆丆俙侾係丄俙俈丄俙俇丄俙侽偟偐宷偑偭偰偍傜偢

俙侾俆丄俙侾係偼乛俤倃俵侾丄俀梡偱丄俙俈丄俙俇丄俙侽偑億乕僩梡偵側傝傑偡

偟偨偑偭偰億乕僩偼侽係侽俫偛偲嬫愗傜傟傑偡

奼挘僐僱僋僞偵偼乛俲俛俽俤俴偲俙侽乣俙俀偑偁傞偺偱

億乕僩侽俠侽俫埲崀偺億乕僩偼壓埵係價僢僩偼侽乣俈傑偱惂屼偱偒傑偡丅

丂侽侽侽俫乣侽俁俥俫丗僐儞僩儘乕儖乮枹巊梡乯

丂侽係侽俫乣侽俈俥俫丗俹俽俧乛倁俢俹

丂侽俉侽俫乣侽俛俥俫丗倁俢俹

丂侽俠侽俫乣侽俥俥俫丗俰俷倄抂巕乛奼挘僐僱僋僞乮俥俵亅俈侽丄俽俲亅侾侾侽侽乯

丂

侽俁俤俫丗俵俙俼俲丂III偱偼枹巊梡

丂俵俙俼俲丂III偱偼僇乕僩儕僢僕偲僇乕僪偺暪梡丄杮懱撪俼俙俵偲奼挘俼俙俵乮侽俠侽侽侽俫埲崀乯偺巊梡傪

丂夞楬偱嬛巭傪寛傔偰偄傑偡偑儅僗僞乕僔僗僥儉埲崀偱偼偙偺億乕僩傪巊梡偟偰

丂僇乕僩儕僢僕傗杮懱撪俼俙俵偺愗傝姺偊摍傪峴偄傑偡

丂億乕僩侽俁俤俫偲億乕僩侽俁俥俫偑俵俙俼俲丂III偲儅僗僞乕僔僗僥儉偺戝偒側堘偄偵側傝

丂僴乕僪傛傝側偺偑俵俙俼俲丂III丄僜僼僩傛傝偱億乕僩侽俁俤俫偲億乕僩侽俁俥俫傪巊梡偡傞偺偑儅僗僞乕僔僗僥儉偲偄偊傑偡丅

丂俵俙俼俲丂III偱偼枹巊梡側偺偱僨乕僞曐帩偝傟偰偄側偄偺偱偡偑撉傓偨傃偵僨乕僞偑曄壔偟傑偡

丂儅僗僞乕僔僗僥儉偱偼巊梡偟偰偄傑偡偑彂偒崬傒梡億乕僩側偺偱撉傓偲侽俥俥俫偵側傝傑偡

丂偦偺堊偵儅僗僞乕僔僗僥儉婲摦偺僗儘僢僩僠僃僢僋偱億乕僩侽俁俤俫偑儚乕僋侽俠侽侽侽俫偺撪梕偵側傝

丂俥俵壒尮傪巊梡偡傞応崌偵偙偺侽俠侽侽侽俫傪撉傫偱億乕僩侽俁俤俫乮俰俷倄抂巕嬛巭乯偵偡傞帠偱

丂傾僋僙僗偡傞帠偵側傝傑偡

丂

侽俁俥俫丗俵俙俼俲丂III偱偼枹巊梡

丂丂丂丂丂儅僗僞乕僔僗僥儉偱偼儊儌儕丄俰俷倄抂巕乛俥俵儐僯僢僩偺惂屼傪峴偄傑偡

丂

侽俈俤俫丗尰嵼偺倁僇僂儞僞乕乮擖椡乯

侽俈俥俫丗尰嵼偺俫僇僂儞僞乕乮擖椡乯乛俹俽俧乮弌椡乯

丂

侽俛俤俫乣侽俛俥俫丗倁俢俹

丂

億乕僩侽俠侽俫乣侽俠侾俫丗俰俷倄抂巕乮儈儔乕乯

丂僨僐乕僪偝傟偰偄側偄偺偱億乕僩侽俢俠俫乣侽俢俢俫偺儈儔乕偵側傝傑偡乮奼挘抂巕偵壗傕宷偘側偄応崌乯

丂晄巚媍側偍忛僺僢僩億僢僩偱偼億乕僩侽俠侽俫乣侽俠侾俫傪巊梡偟偰偄傑偡

丂偨偩偟俥俵儐僯僢僩傪晅偗偰偄傞応崌偼摦嶌偑偍偐偟偔側偭偰偟傑偆偺偱巊梡偟側偄曽偑椙偄偱偡

丂

侽俢俠俫丗俰俷倄抂巕乮擖椡乯

丂倓俈丗俰俷倄俀丂俀僺儞乮俢俷倂俶丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俇丗俰俷倄俀丂侾僺儞乮倀俹丂丂丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俆丗俰俷倄侾丂俋僺儞乮俀儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓係丗俰俷倄侾丂俇僺儞乮侾儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俁丗俰俷倄侾丂係僺儞乮俼俬俧俫俿乯丂侾亖僆僼丄侽亖僆儞

丂倓俀丗俰俷倄侾丂俁僺儞乮俴俤俥俿丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侾丗俰俷倄侾丂俀僺儞乮俢俷倂俶丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侽丗俰俷倄侾丂侾僺儞乮倀俹丂丂丂乯丂侾亖僆僼丄侽亖僆儞

丂

侽俢俢俫丗俰俷倄抂巕亄俠俷俶抂巕乮擖椡乯

丂倓俈丗俬俠俋丂俈係俴俽俀俆俈偺13僺儞丂侾偱屌掕乮枹巊梡乯

丂倓俇丗俬俠俋丂俈係俴俽俀俆俈偺10僺儞丂侾偱屌掕乮枹巊梡乯

丂倓俆丗俬俠俋丂俈係俴俽俀俆俈偺俇僺儞丂侾偱屌掕乮枹巊梡乯

丂倓係丗俠俷俶抂巕丂丂丂丂丂丂丂丂丂丂丂侾亖僆僼丄侽亖僆儞

丂倓俁丗俰俷倄俀丂俋僺儞乮俀儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俀丗俰俷倄俀丂俇僺儞乮侾儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侾丗俰俷倄俀丂係僺儞乮俼俬俧俫俿乯丂侾亖僆僼丄侽亖僆儞

丂倓侽丗俰俷倄俀丂俁僺儞乮俴俤俥俿丂乯丂侾亖僆僼丄侽亖僆儞

丂

丂仏億乕僩侽俢俢俫傪傒偰擔杮偺僴乕僪偐奀奜偺僴乕僪偑敾抐弌棃傑偡

丂丂億乕僩侽俁俥俫偵侽俥俆俫傪弌椡偟偰億乕僩侽俢俢俫傪尒傞

丂丂億乕僩侽俁俥俫偵侽俆俆俫傪弌椡偟偰億乕僩侽俢俢俫傪尒傞帠偱敾抐弌棃傑偡丅

丂丂丂俵俙俼俲丂III偺応崌

丂丂丂丂億乕僩侽俁俥俫偼巊梡偟偰偄側偄偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈乣俇偼侾侾偱屌掕

丂

丂丂丂擔杮偺儅僗僞乕僔僗僥儉偺応崌

丂丂丂丂億乕僩侽俁俥俫偺倓俁乣侾偺撪梕偼侽側偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈乣俇偼俀夞偲傕侽侽

丂

丂丂丂奀奜偺儅僗僞乕僔僗僥儉偺応崌

丂丂丂丂俰俷倄抂巕偺俈僺儞偺愝掕偺抣偑擖傞偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈亅俇偼侾侾偲侽侽

丂

丂丂丂侾侾偐傜侾侾側傜俵俙俼俲丂III

丂丂丂侽侽偐傜侽侽側傜擔杮偺儅僗僞乕僔僗僥儉

丂丂丂侾侾偐傜侽侽偵曄壔偡傞側傜奀奜偺儅僗僞乕僔僗僥儉偵側傝傑偡

丂

侽俢俠俫乣侽俢俥俫丗俽俲亅侾侾侽侽乮僆僾僔儑儞偺僉乕儃乕僪乯

丂俉俀俆俆傪巊梡偟偰偍傝丄侽俢俠俫乣侽俢俥俫偑巊梡斖埻

丂俬乛俷億乕僩偑僼儖僨乕僐乕僪偝傟偰偄側偄偺偱俰俷倄抂巕偲廳暋偟偰偄傑偡

丂偦偺堊捠忢俽俲亅侾侾侽侽傪傾僋僙僗偡傞応崌偼

丂杮懱撪偺俰俷倄抂巕傪嬛巭偡傞傛偆偵側偭偰偄傑偡丅

丂僉乕僙儗僋僩斣崋侽俈傪慖戰偟偨偲偒偵

丂僉乕儃乕僪偑巊梡嬛巭偵側傝俰俷倄抂巕傪巊梡偡傞傛偆偵側傝傑偡

丂

丂俵俙俼俲丂III扨懱偩偲億乕僩僨乕僞偺曐帩乮儔僢僠乯偼偝傟側偄偺偱

丂傑偢億乕僩侽俢俥俫乮俉俀俆俆俠倂乯偵侽俋俀俫傪彂偒偙傒擖弌椡偺愝掕偟偰偐傜

丂侽俢俤俫乮俉俀俆俆俹俠乯偵侽侽侽俫傪彂偒偙傫偱丄億乕僩侽俢俤俫傪撉傓

丂丂侽俥俥俫側傜俵俙俼俲丂III偺傒丄

丂丂侽侽侽俫側傜俵俙俼俲丂III亄俽俲亅侾侾侽侽偲側傝傑偡

丂

丂杮懱偺傒偩偲僨乕僞偼曐帩偝傟側偄偺偱侽侽侽俫傪彂偒崬傫偱傕侽俥俥俫偵側偭偰偟傑偄傑偡偑

丂俽俲亅侾侾侽侽愙懕偱偼俉俀俆俆偵傛偭偰侽侽侽俫偺彂偒崬傒偑惓忢偵峴傢傟傞偺傪棙梡偟偰敾抐偟傑偡

丂

侽俥侽俫乣侽俥俀俫:俥俵亅俈侽乮僆僾僔儑儞偺俥俵壒尮儐僯僢僩倄俵俀侾係俁傪巊梡乯

丂俰俷倄抂巕傗俽俲亅侾侾侽侽偲廳暋偟偰偄傑偡乮俽俲亅侾侾侽侽偲嫟梡晄壜乯

丂億乕僩侽俥侽俫丄侽俥侾俫偼俰俷倄抂巕偲廳側傞偺偱偡偑

丂俰俷倄抂巕偼擖椡偺傒偱俥俵儐僯僢僩偼婎杮弌椡偵側傝傑偡

丂侽俥俀俫偑擖椡偵側傞偺偱侽俢俠俫偲廳側傝傑偡偑俥俵儐僯僢僩偺夞楬偱俰俷倄抂巕偼巊梡嬛巭偵側傝傑偡

丂擔杮偺儅僗僞乕僔僗僥儉偱偼億乕僩侽俁俤俫偺倓俀傪侾偵偟偰俰俷倄抂巕傪嬛巭偵偟偰

丂愙懕僠僃僢僋傪峴偄傑偡乮俀庬椶偺愙懕僠僃僢僋偑昁梫乯

丂

俼俷俵僄儕傾偼僇乕僪丄僇乕僪儕僢僕偵傛偭偰梕検偑曄傝傑偡

侽俉侽侽侽俫偵偼俼俙俵傗俼俷俵傪嵹偣傞偙偲偑偱偒傑偡丅

杮懱撪偺俼俙俵偼俛俁抂巕傪侾偵偡傞帠偵傛偭偰巊梡嬛巭偵弌棃傑偡乮儅僗僞乕僔僗僥儉偼峏偵僜僼僩偱愗傝姺偊壜乯

儅僗僞乕僔僗僥儉偵偼俁偮偺僗儘僢僩乮僇乕僩儕僢僕丄僇乕僪丄奼挘抂巕乯偵傛偭偰儊儌儕傪嵹偣傞帠偑弌棃傑偡

僗儘僢僩偺愗傝姺偊偼億乕僩侽俁俤俫傪巊梡偟偰偄傑偡偑俵俙俼俲丂III偱偼億乕僩傪擿偄偰傕侽俥俥俫偵側傝傑偡

儅僗僞乕僔僗僥儉偱偼俬俹俴婲摦丄僗儘僢僩僠僃僢僋丄愗傝姺偊偱巊梡偟偨億乕僩侽俁俤俫偺撪梕偑

侽俠侽侽侽俫偵弌椡丄棙梡偟傑偡乮儅僗僞乕僔僗僥儉偺傒乯

丂

儊僈俼俷俵偼儊儌儕儅僢僷傪僇乕僩儕僢僕撪偵帩偪杮懱撪偵偼僶儞僋愗傝姺偊偺婡擻偼偁傝傑偣傫

傑偨婔偮偐偺儊儌儕儅僢僷偑偁傝傑偡偑惂屼偺曽朄偼偳偺僇乕僩儕僢僕傕傎傏摨偠偱

僶儞僋愗傝懼偊曽幃偱儊儌儕儅僢僾丒霓丒俬乛俷偵傛偭偰惂屼偝傟傑偡

傾僪儗僗偼侽俥俥俥俠俫乣侽俥俥俥俥俫傑偱巊梡偟偰偍傝丄侾俇俲俛偛偲愗傝懼傢傝傑偡

丂

俁俢傾僟僾僞偼侽俥俥俥俉俫乣侽俥俥俥俛俫偺斖埻偱

僜僼僩偱偼侽俥俥俥俛俫傪巊梡偟偰偄傑偡乮懠偺傾僪儗僗偼儈儔乕乯

僼儖僨僐乕僪偼偝傟偰偄側偄偺偱杮懱撪偺儚乕僋俼俙俵偺侽俢俥俥俠俫乣侽俢俥俥俥俫偼

巊梡弌棃傑偣傫乮儅僢僷偺儈儔乕偵側偭偰偄傑偡乯

丂

丂侽俥俥俥俉俫乣侽俥俥俥俛俫丗俁俢僔僗僥儉偱巊梡 捠忢侽俥俥俥俛俫偺傒巊梡乮倓侽偱嵍丄塃偺愗傝懼偊丠)

丂侽俥俥俥俠俫丂丂丂丂丂丂丂丗庡偵僶僢僋傾僢僾俼俙俵偺愗傝姺偊

丂侽俥俥俥俢俫丂丂丂丂丂丂丂丗杮懱偺侽侽侽侽侽俫乣侽俁俥俥俥俫偵僶儞僋傪慖戰

丂侽俥俥俥俤俫丂丂丂丂丂丂丂丗杮懱偺侽係侽侽侽俫乣侽俈俥俥俥俫偵僶儞僋傪慖戰

丂侽俥俥俥俥俫丂丂丂丂丂丂丂丗杮懱偺侽俉侽侽侽俫乣侽俛俥俥俥俫偵僶儞僋傪慖戰

丂

丂

俬乛俷億乕僩

丂

倁俢俹撪偱億乕僩惂屼傪峴偭偰偍傝

巊梡傾僪儗僗僶僗偼俙侾俆丆俙侾係丄俙俈丄俙俇丄俙侽偟偐宷偑偭偰偍傜偢

俙侾俆丄俙侾係偼乛俤倃俵侾丄俀梡偱丄俙俈丄俙俇丄俙侽偑億乕僩梡偵側傝傑偡

偟偨偑偭偰億乕僩偼侽係侽俫偛偲嬫愗傜傟傑偡

奼挘僐僱僋僞偵偼乛俲俛俽俤俴偲俙侽乣俙俀偑偁傞偺偱

億乕僩侽俠侽俫埲崀偺億乕僩偼壓埵係價僢僩偼侽乣俈傑偱惂屼偱偒傑偡丅

丂侽侽侽俫乣侽俁俥俫丗僐儞僩儘乕儖乮枹巊梡乯

丂侽係侽俫乣侽俈俥俫丗俹俽俧乛倁俢俹

丂侽俉侽俫乣侽俛俥俫丗倁俢俹

丂侽俠侽俫乣侽俥俥俫丗俰俷倄抂巕乛奼挘僐僱僋僞乮俥俵亅俈侽丄俽俲亅侾侾侽侽乯

丂

侽俁俤俫丗俵俙俼俲丂III偱偼枹巊梡

丂俵俙俼俲丂III偱偼僇乕僩儕僢僕偲僇乕僪偺暪梡丄杮懱撪俼俙俵偲奼挘俼俙俵乮侽俠侽侽侽俫埲崀乯偺巊梡傪

丂夞楬偱嬛巭傪寛傔偰偄傑偡偑儅僗僞乕僔僗僥儉埲崀偱偼偙偺億乕僩傪巊梡偟偰

丂僇乕僩儕僢僕傗杮懱撪俼俙俵偺愗傝姺偊摍傪峴偄傑偡

丂億乕僩侽俁俤俫偲億乕僩侽俁俥俫偑俵俙俼俲丂III偲儅僗僞乕僔僗僥儉偺戝偒側堘偄偵側傝

丂僴乕僪傛傝側偺偑俵俙俼俲丂III丄僜僼僩傛傝偱億乕僩侽俁俤俫偲億乕僩侽俁俥俫傪巊梡偡傞偺偑儅僗僞乕僔僗僥儉偲偄偊傑偡丅

丂俵俙俼俲丂III偱偼枹巊梡側偺偱僨乕僞曐帩偝傟偰偄側偄偺偱偡偑撉傓偨傃偵僨乕僞偑曄壔偟傑偡

丂儅僗僞乕僔僗僥儉偱偼巊梡偟偰偄傑偡偑彂偒崬傒梡億乕僩側偺偱撉傓偲侽俥俥俫偵側傝傑偡

丂偦偺堊偵儅僗僞乕僔僗僥儉婲摦偺僗儘僢僩僠僃僢僋偱億乕僩侽俁俤俫偑儚乕僋侽俠侽侽侽俫偺撪梕偵側傝

丂俥俵壒尮傪巊梡偡傞応崌偵偙偺侽俠侽侽侽俫傪撉傫偱億乕僩侽俁俤俫乮俰俷倄抂巕嬛巭乯偵偡傞帠偱

丂傾僋僙僗偡傞帠偵側傝傑偡

丂

侽俁俥俫丗俵俙俼俲丂III偱偼枹巊梡

丂丂丂丂丂儅僗僞乕僔僗僥儉偱偼儊儌儕丄俰俷倄抂巕乛俥俵儐僯僢僩偺惂屼傪峴偄傑偡

丂

侽俈俤俫丗尰嵼偺倁僇僂儞僞乕乮擖椡乯

侽俈俥俫丗尰嵼偺俫僇僂儞僞乕乮擖椡乯乛俹俽俧乮弌椡乯

丂

侽俛俤俫乣侽俛俥俫丗倁俢俹

丂

億乕僩侽俠侽俫乣侽俠侾俫丗俰俷倄抂巕乮儈儔乕乯

丂僨僐乕僪偝傟偰偄側偄偺偱億乕僩侽俢俠俫乣侽俢俢俫偺儈儔乕偵側傝傑偡乮奼挘抂巕偵壗傕宷偘側偄応崌乯

丂晄巚媍側偍忛僺僢僩億僢僩偱偼億乕僩侽俠侽俫乣侽俠侾俫傪巊梡偟偰偄傑偡

丂偨偩偟俥俵儐僯僢僩傪晅偗偰偄傞応崌偼摦嶌偑偍偐偟偔側偭偰偟傑偆偺偱巊梡偟側偄曽偑椙偄偱偡

丂

侽俢俠俫丗俰俷倄抂巕乮擖椡乯

丂倓俈丗俰俷倄俀丂俀僺儞乮俢俷倂俶丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俇丗俰俷倄俀丂侾僺儞乮倀俹丂丂丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俆丗俰俷倄侾丂俋僺儞乮俀儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓係丗俰俷倄侾丂俇僺儞乮侾儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俁丗俰俷倄侾丂係僺儞乮俼俬俧俫俿乯丂侾亖僆僼丄侽亖僆儞

丂倓俀丗俰俷倄侾丂俁僺儞乮俴俤俥俿丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侾丗俰俷倄侾丂俀僺儞乮俢俷倂俶丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侽丗俰俷倄侾丂侾僺儞乮倀俹丂丂丂乯丂侾亖僆僼丄侽亖僆儞

丂

侽俢俢俫丗俰俷倄抂巕亄俠俷俶抂巕乮擖椡乯

丂倓俈丗俬俠俋丂俈係俴俽俀俆俈偺13僺儞丂侾偱屌掕乮枹巊梡乯

丂倓俇丗俬俠俋丂俈係俴俽俀俆俈偺10僺儞丂侾偱屌掕乮枹巊梡乯

丂倓俆丗俬俠俋丂俈係俴俽俀俆俈偺俇僺儞丂侾偱屌掕乮枹巊梡乯

丂倓係丗俠俷俶抂巕丂丂丂丂丂丂丂丂丂丂丂侾亖僆僼丄侽亖僆儞

丂倓俁丗俰俷倄俀丂俋僺儞乮俀儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓俀丗俰俷倄俀丂俇僺儞乮侾儃僞儞丂乯丂侾亖僆僼丄侽亖僆儞

丂倓侾丗俰俷倄俀丂係僺儞乮俼俬俧俫俿乯丂侾亖僆僼丄侽亖僆儞

丂倓侽丗俰俷倄俀丂俁僺儞乮俴俤俥俿丂乯丂侾亖僆僼丄侽亖僆儞

丂

丂仏億乕僩侽俢俢俫傪傒偰擔杮偺僴乕僪偐奀奜偺僴乕僪偑敾抐弌棃傑偡

丂丂億乕僩侽俁俥俫偵侽俥俆俫傪弌椡偟偰億乕僩侽俢俢俫傪尒傞

丂丂億乕僩侽俁俥俫偵侽俆俆俫傪弌椡偟偰億乕僩侽俢俢俫傪尒傞帠偱敾抐弌棃傑偡丅

丂丂丂俵俙俼俲丂III偺応崌

丂丂丂丂億乕僩侽俁俥俫偼巊梡偟偰偄側偄偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈乣俇偼侾侾偱屌掕

丂

丂丂丂擔杮偺儅僗僞乕僔僗僥儉偺応崌

丂丂丂丂億乕僩侽俁俥俫偺倓俁乣侾偺撪梕偼侽側偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈乣俇偼俀夞偲傕侽侽

丂

丂丂丂奀奜偺儅僗僞乕僔僗僥儉偺応崌

丂丂丂丂俰俷倄抂巕偺俈僺儞偺愝掕偺抣偑擖傞偺偱

丂丂丂丂億乕僩侽俢俢俫偺倓俈亅俇偼侾侾偲侽侽

丂

丂丂丂侾侾偐傜侾侾側傜俵俙俼俲丂III

丂丂丂侽侽偐傜侽侽側傜擔杮偺儅僗僞乕僔僗僥儉

丂丂丂侾侾偐傜侽侽偵曄壔偡傞側傜奀奜偺儅僗僞乕僔僗僥儉偵側傝傑偡

丂

侽俢俠俫乣侽俢俥俫丗俽俲亅侾侾侽侽乮僆僾僔儑儞偺僉乕儃乕僪乯

丂俉俀俆俆傪巊梡偟偰偍傝丄侽俢俠俫乣侽俢俥俫偑巊梡斖埻

丂俬乛俷億乕僩偑僼儖僨乕僐乕僪偝傟偰偄側偄偺偱俰俷倄抂巕偲廳暋偟偰偄傑偡

丂偦偺堊捠忢俽俲亅侾侾侽侽傪傾僋僙僗偡傞応崌偼

丂杮懱撪偺俰俷倄抂巕傪嬛巭偡傞傛偆偵側偭偰偄傑偡丅

丂僉乕僙儗僋僩斣崋侽俈傪慖戰偟偨偲偒偵

丂僉乕儃乕僪偑巊梡嬛巭偵側傝俰俷倄抂巕傪巊梡偡傞傛偆偵側傝傑偡

丂

丂俵俙俼俲丂III扨懱偩偲億乕僩僨乕僞偺曐帩乮儔僢僠乯偼偝傟側偄偺偱

丂傑偢億乕僩侽俢俥俫乮俉俀俆俆俠倂乯偵侽俋俀俫傪彂偒偙傒擖弌椡偺愝掕偟偰偐傜

丂侽俢俤俫乮俉俀俆俆俹俠乯偵侽侽侽俫傪彂偒偙傫偱丄億乕僩侽俢俤俫傪撉傓

丂丂侽俥俥俫側傜俵俙俼俲丂III偺傒丄

丂丂侽侽侽俫側傜俵俙俼俲丂III亄俽俲亅侾侾侽侽偲側傝傑偡

丂

丂杮懱偺傒偩偲僨乕僞偼曐帩偝傟側偄偺偱侽侽侽俫傪彂偒崬傫偱傕侽俥俥俫偵側偭偰偟傑偄傑偡偑

丂俽俲亅侾侾侽侽愙懕偱偼俉俀俆俆偵傛偭偰侽侽侽俫偺彂偒崬傒偑惓忢偵峴傢傟傞偺傪棙梡偟偰敾抐偟傑偡

丂

侽俥侽俫乣侽俥俀俫:俥俵亅俈侽乮僆僾僔儑儞偺俥俵壒尮儐僯僢僩倄俵俀侾係俁傪巊梡乯

丂俰俷倄抂巕傗俽俲亅侾侾侽侽偲廳暋偟偰偄傑偡乮俽俲亅侾侾侽侽偲嫟梡晄壜乯

丂億乕僩侽俥侽俫丄侽俥侾俫偼俰俷倄抂巕偲廳側傞偺偱偡偑

丂俰俷倄抂巕偼擖椡偺傒偱俥俵儐僯僢僩偼婎杮弌椡偵側傝傑偡

丂侽俥俀俫偑擖椡偵側傞偺偱侽俢俠俫偲廳側傝傑偡偑俥俵儐僯僢僩偺夞楬偱俰俷倄抂巕偼巊梡嬛巭偵側傝傑偡

丂擔杮偺儅僗僞乕僔僗僥儉偱偼億乕僩侽俁俤俫偺倓俀傪侾偵偟偰俰俷倄抂巕傪嬛巭偵偟偰

丂愙懕僠僃僢僋傪峴偄傑偡乮俀庬椶偺愙懕僠僃僢僋偑昁梫乯

丂

丂

侾俵倐倝倲僇乕僩儕僢僕丂171-5363乮俿倄俹俤亅俥乯偺夞楬恾

丂

侾俵倐倝倲僇乕僩儕僢僕丂171-5363乮俿倄俹俤亅俥乯偺夞楬恾

丂

丂

僗儁乕僗僴儕傾乕傗傾僂僩儔儞偱巊梡偝傟偰偄傑偡丅

偝傜偵戝梕検偺俼俷俵傕僒億乕僩偱偒傞傛偆偵側傝丄儅僢僷乕偺傾僋僙僗傕彮偟奼挘偝傟偰偄傑偡丅

偨偩偟丄婎杮揑側傾僋僙僗曽朄偼摨偠偱丄奀奜偺儅僗僞乕僔僗僥儉偺俼俷俵僠僃僢僋偺搒崌偱

摨偠曽朄偱側偄偲僠僃僢僋偱偒側偄堊偩偲巚傢傟傑偡丅

丂

俀俵倐倝倲僇乕僩儕僢僕丂僗儁乕僗僴儕傾乕丂侾俈侾亅俆係係侽乮俀俵仏侾僶乕僕儑儞乯偺夞楬恾

僗儁乕僗僴儕傾乕傗傾僂僩儔儞偱巊梡偝傟偰偄傑偡丅

偝傜偵戝梕検偺俼俷俵傕僒億乕僩偱偒傞傛偆偵側傝丄儅僢僷乕偺傾僋僙僗傕彮偟奼挘偝傟偰偄傑偡丅

偨偩偟丄婎杮揑側傾僋僙僗曽朄偼摨偠偱丄奀奜偺儅僗僞乕僔僗僥儉偺俼俷俵僠僃僢僋偺搒崌偱

摨偠曽朄偱側偄偲僠僃僢僋偱偒側偄堊偩偲巚傢傟傑偡丅

丂

俀俵倐倝倲僇乕僩儕僢僕丂僗儁乕僗僴儕傾乕丂侾俈侾亅俆係係侽乮俀俵仏侾僶乕僕儑儞乯偺夞楬恾

摨偠偔僗儁乕僗僴儕傾乕偺俀俵俛倝倲俼俷俵仏侾僶乕僕儑儞偱偡丅乮屻婜僶乕僕儑儞丠乯

摨偠儊儌儕儅僢僷乕傪巊梡偟偰偄傞傛偆側偺偱偡偑丄庒姳攝慄偑堘偭偰偄傑偡

偙偙偱堘偆売強偼儅僢僷乕偺俁侾俆亅俆俁俀俆偺俀俆僺儞偺擖椡偲乛俠俤侽丄乛俠俤侾偺弌椡晹暘偱偡

巆傝偺嬻敀晹暘偼嫲傜偔丄僶儞僋愗傝姺偊偺乛俠俤偲丄偦偺弌椡偺僞僀僾偺慖戰偵巊傢傟傞偲巚傢傟傑偡

俼俷俵偺柤徧俵俹俼亅侾侽係侾偑僗儁乕僗僴儕乕傾傪巜偟偰丄巆傝偺侾働僞偑俼俷俵偺庬椶丠

儅僢僷乕偵宷偑傞僨乕僞僶僗偼倓俈偲倓係乣侽側偺偱倓俈偑俼俙俵偺僀僱乕僽儖丄

倓係乣侽偑僶儞僋値値乮侽侽侽俫乣侽侾俥俫乯偵側傞偲巚傢傟傑偡

傑偨丄搵嵹壜擻偺儊儌儕偼侾俵俛倝倲丄俀俵俛倝倲丄係俵俛倝倲偱嵟戝儊儌儕偼係俵俛倝倲偺傛偆偱偡丅

丂

丂

俀俵倐倝倲僇乕僩儕僢僕丂擬媴峛巕墍丂侾俈侾亅俆係係侾乮俀俵俼俷俵丂俁俀僺儞僶乕僕儑儞乯偺夞楬恾

摨偠偔僗儁乕僗僴儕傾乕偺俀俵俛倝倲俼俷俵仏侾僶乕僕儑儞偱偡丅乮屻婜僶乕僕儑儞丠乯

摨偠儊儌儕儅僢僷乕傪巊梡偟偰偄傞傛偆側偺偱偡偑丄庒姳攝慄偑堘偭偰偄傑偡

偙偙偱堘偆売強偼儅僢僷乕偺俁侾俆亅俆俁俀俆偺俀俆僺儞偺擖椡偲乛俠俤侽丄乛俠俤侾偺弌椡晹暘偱偡

巆傝偺嬻敀晹暘偼嫲傜偔丄僶儞僋愗傝姺偊偺乛俠俤偲丄偦偺弌椡偺僞僀僾偺慖戰偵巊傢傟傞偲巚傢傟傑偡

俼俷俵偺柤徧俵俹俼亅侾侽係侾偑僗儁乕僗僴儕乕傾傪巜偟偰丄巆傝偺侾働僞偑俼俷俵偺庬椶丠

儅僢僷乕偵宷偑傞僨乕僞僶僗偼倓俈偲倓係乣侽側偺偱倓俈偑俼俙俵偺僀僱乕僽儖丄

倓係乣侽偑僶儞僋値値乮侽侽侽俫乣侽侾俥俫乯偵側傞偲巚傢傟傑偡

傑偨丄搵嵹壜擻偺儊儌儕偼侾俵俛倝倲丄俀俵俛倝倲丄係俵俛倝倲偱嵟戝儊儌儕偼係俵俛倝倲偺傛偆偱偡丅

丂

丂

俀俵倐倝倲僇乕僩儕僢僕丂擬媴峛巕墍丂侾俈侾亅俆係係侾乮俀俵俼俷俵丂俁俀僺儞僶乕僕儑儞乯偺夞楬恾

丂32僺儞偺儅僗僋俼俷俵傪巊梡偟偰偄傑偡丅

丂

係俵倐倝倲僇乕僩儕僢僕丂傾僼僞乕僶乕僫乕丂侾俈侾亅俆俆俉俋俢乮俀俵仏俀乯偺夞楬恾

丂32僺儞偺儅僗僋俼俷俵傪巊梡偟偰偄傑偡丅

丂

係俵倐倝倲僇乕僩儕僢僕丂傾僼僞乕僶乕僫乕丂侾俈侾亅俆俆俉俋俢乮俀俵仏俀乯偺夞楬恾

丂

係俵倐倝倲僇乕僩儕僢僕丂僼傽儞僞僔乕僗僞乕丂侾俈侾亅俆俆俉俁乮係俵亄俇係俲俛倝倲俽亅俼俙俵乯偺夞楬恾

丂

丂

僇乕僩儕僢僕撪偺婎斅偺庬椶

侾俈侾亅俆俁俇俀丂丂丂丗俿倄俹俤亅俶丂儅僢僷乕撪憼侾俵俛倝倲丂俼俷俵

侾俈侾亅俆俁俇俁亅侽侾丗俿倄俹俤亅俥丂俁侾俆亅俆俀侽俉亄侾俵俛倝倲丂俼俷俵

侾俈侾亅俆係俁俋丂丂丂丗俁侾俆亅俆俀俁俆亄侾俵俛倝倲丂俼俷俵仏俀

侾俈侾亅俆係係侽丂丂丂丗俁侾俆亅俆俀俁俆亄俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆侽侽丂丂丂丗俁侾俆亅俆俀俁俆亄侾俵俛倝倲丂俼俷俵亄俇係俲俽俼俙俵亄俵俛俁俈俈侾

侾俈侾亅俆俆侽俇丂丂丂丗儅僢僷乕撪憼俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆侾俉丂丂丂丗儅僢僷乕撪憼侾俵俛倝倲丂俼俷俵

侾俈侾亅俆侾俈俈丂丂丂丗俽俧亅侾侽侽侽梡偺婎斅傪僕儍儞僷乕慄傪巊偄俿倄俹俤亅俶偲摨條偵偟偨傕偺

侾俈侾亅俆俆俇係丂丂丂丗儅僢僷乕撪憼俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆俉俋俢丂丂丗俁侾俆亅俆俀俁俆亄俀俵俛倝倲丂俼俷俵仏俀

侾俈侾亅俆俆俉俁丂丂丂丗俁侾俆亅俆俀俁俆亄係俵俛倝倲丂俼俷俵亄俇係俲俽俼俙俵亄俿俆俀俋俥

丂

丂

係俵倐倝倲僇乕僩儕僢僕丂僼傽儞僞僔乕僗僞乕丂侾俈侾亅俆俆俉俁乮係俵亄俇係俲俛倝倲俽亅俼俙俵乯偺夞楬恾

丂

丂

僇乕僩儕僢僕撪偺婎斅偺庬椶

侾俈侾亅俆俁俇俀丂丂丂丗俿倄俹俤亅俶丂儅僢僷乕撪憼侾俵俛倝倲丂俼俷俵

侾俈侾亅俆俁俇俁亅侽侾丗俿倄俹俤亅俥丂俁侾俆亅俆俀侽俉亄侾俵俛倝倲丂俼俷俵

侾俈侾亅俆係俁俋丂丂丂丗俁侾俆亅俆俀俁俆亄侾俵俛倝倲丂俼俷俵仏俀

侾俈侾亅俆係係侽丂丂丂丗俁侾俆亅俆俀俁俆亄俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆侽侽丂丂丂丗俁侾俆亅俆俀俁俆亄侾俵俛倝倲丂俼俷俵亄俇係俲俽俼俙俵亄俵俛俁俈俈侾

侾俈侾亅俆俆侽俇丂丂丂丗儅僢僷乕撪憼俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆侾俉丂丂丂丗儅僢僷乕撪憼侾俵俛倝倲丂俼俷俵

侾俈侾亅俆侾俈俈丂丂丂丗俽俧亅侾侽侽侽梡偺婎斅傪僕儍儞僷乕慄傪巊偄俿倄俹俤亅俶偲摨條偵偟偨傕偺

侾俈侾亅俆俆俇係丂丂丂丗儅僢僷乕撪憼俀俵俛倝倲丂俼俷俵

侾俈侾亅俆俆俉俋俢丂丂丗俁侾俆亅俆俀俁俆亄俀俵俛倝倲丂俼俷俵仏俀

侾俈侾亅俆俆俉俁丂丂丂丗俁侾俆亅俆俀俁俆亄係俵俛倝倲丂俼俷俵亄俇係俲俽俼俙俵亄俿俆俀俋俥

丂

丂

倁亅俼俙俵廃傝偺夞楬恾

丂

倁亅俼俙俵廃傝偺夞楬恾

丂

丂

俰俷倄抂巕廃傝偺夞楬恾

丂

丂

俰俷倄抂巕廃傝偺夞楬恾

丂

楢幩儐僯僢僩乮俼俥亅侾俆侽乯偺夞楬恾

丂

楢幩儐僯僢僩乮俼俥亅侾俆侽乯偺夞楬恾