SEGA SC-3000

俛俙俽俬俠丂俴俤倁俤俴丂III傊

丂

SEGA SG-3000 偺僗儁僢僋

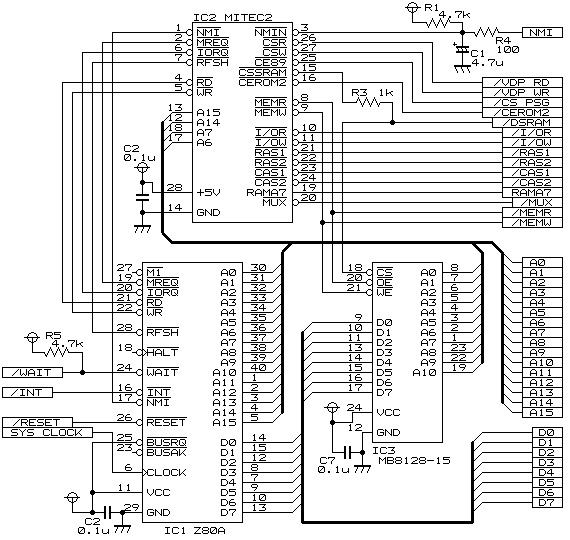

| CPU | D780C-1(Z80A) 3.579MHz |

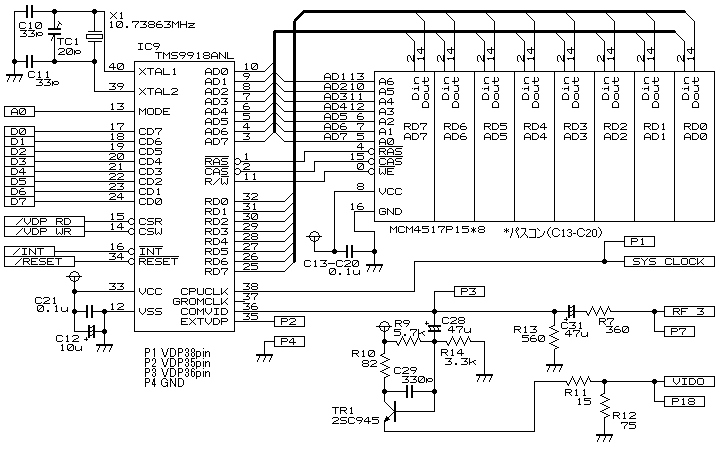

| VDP | TMS9918A |

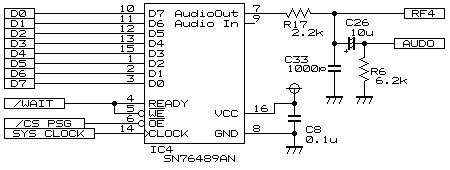

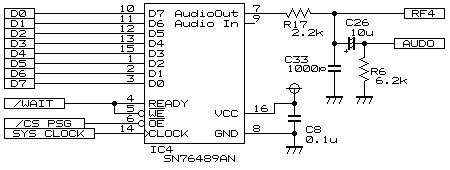

| PSG | SN76489 |

| ROM | 僗儘僢僩偵傛傝嫙媼 |

| RAM | 2KB(奼挘壜) |

| V-RAM | 16KB |

僙僈丒僄儞僞乕僾儔僀僘偝傫偺僷乕僜僫儖僐儞僺儏乕僞帠嬈晹偐傜敪攧偝傟偨掅壙奿僷僜僐儞偱嵟掅尷偺愝寁偼偟偰偄傞丅

奼挘傕怓乆峫椂偝傟偰偄偰俆僗儘僢僩偺奼挘儐僯僢僩偑敪攧偝傟側偐偭偨偺偑夨傗傑傟傞丅

俿倁斣慻偺乭僷僜僐儞塅拡戝嶌愴丂亅丂傾僀僪儖傪媬偊乭偱偼僗億儞僒乕偑僙僈偝傫偩偭偨偺偱僎僗僩偵俽俧亅侾侽侽侽偑憽掓偝傟

斣慻僎乕儉偺僷僜僐儞暉徫偄偼俽俠亅俁侽侽侽傪巊梡偝傟傞

俛俙俽俬俠偑彮偟抶偄偺偲乛俬俶俿傪僼僢僋偵偣偢俼俷俵撪偱屌掕偝傟偰偄傞晄枮偼偁傞丅

偟偐偟杮懱撪俼俙俵傪巊梡嬛巭偵弌棃傞堊丄儊儌儕偑娙扨偵憹愝偱偒傞傛偆偵側偭偰偄傞偺偼椙偄丅

丂

傑偨僇僗僞儉僠僢僾偑俢亅俼俙俵偺儕僼儗僢僔儏丄俬乛俷億乕僩偺僨僐乕僪傪峴偭偰偄傞堊丄撪晹偼僔儞僾儖偵弌棃偰偄傞

俽俠亅侾侽侽侽偐傜俽俠亅俆侽侽侽傑偱偺梊掕偼偁偭偨傜偟偔幚嵺偵敪攧偝傟偨偺偼偙偺俽俠亅俁侽侽侽偩偗偱偁傞

僨傿僗僋僔僗僥儉俽俥亅俈侽侽侽偲摨帪婜偵俠俙俿倁傪棙梡偟偨僱僢僩儚乕僋僔僗僥儉

俽俤俧俙丂俢俷俽偺梊掕傕偁偭偨偑幚尡偩偗偱廔傢偭偨柾條

丂

俠俹倀

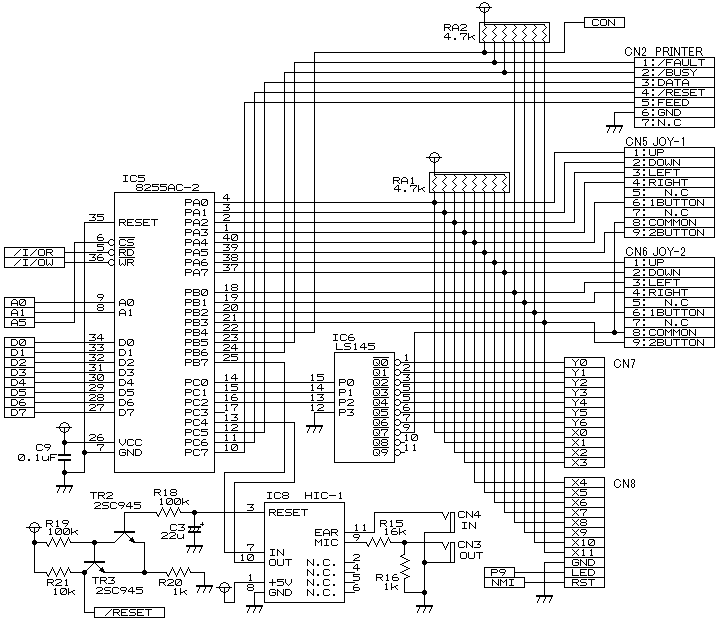

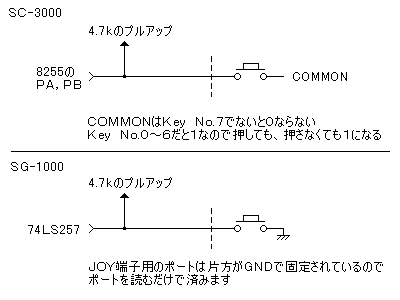

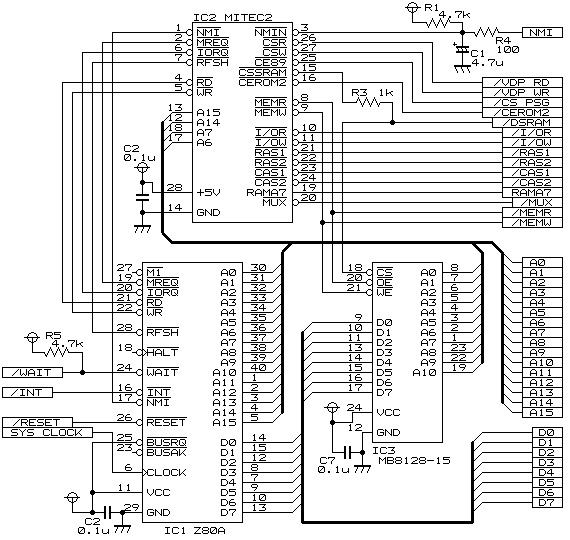

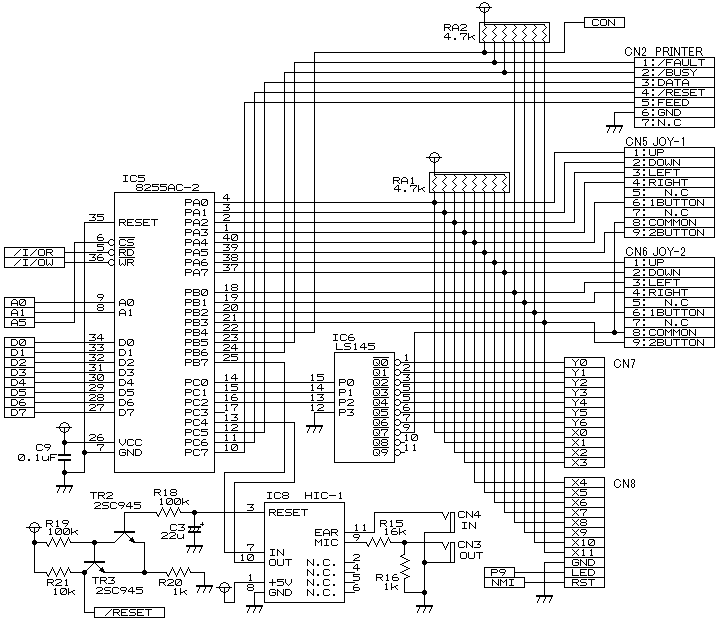

俠俹倀偼俶俤俠偺俹俢俈俉侽亅侾傪巊梡丂僋儘僢僋偼栺俁丏俆俈俋俵俫倸

妱傝崬傒偼儌乕僪侾偱俶俵俬偼俼俤俽俤俿僉乕乮億乕僘僉乕乯丄俬俶俿偼倁俢俹偐傜偺倁俽倄俶俠偵妱傝摉偰傜傟偰偄傑偡

乛俷俽俼俙俵偼杮懱撪偺俽俼俙俵偺乛俠俽偵宷偑偭偰偄偰侾偵偡傞帠偵傛偭偰巊梡嬛巭偵弌棃傑偡

丂

倁俢俹

俠俹倀偼俶俤俠偺俹俢俈俉侽亅侾傪巊梡丂僋儘僢僋偼栺俁丏俆俈俋俵俫倸

妱傝崬傒偼儌乕僪侾偱俶俵俬偼俼俤俽俤俿僉乕乮億乕僘僉乕乯丄俬俶俿偼倁俢俹偐傜偺倁俽倄俶俠偵妱傝摉偰傜傟偰偄傑偡

乛俷俽俼俙俵偼杮懱撪偺俽俼俙俵偺乛俠俽偵宷偑偭偰偄偰侾偵偡傞帠偵傛偭偰巊梡嬛巭偵弌棃傑偡

丂

倁俢俹

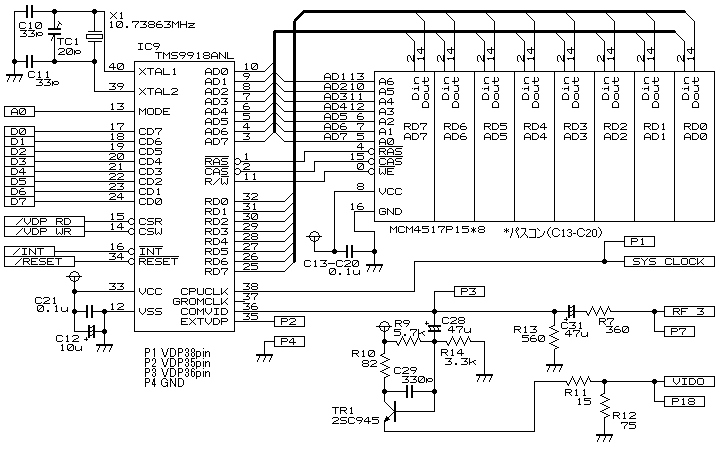

倁俢俹偼俿俬惢俿俵俽俋俋侾俉俙傪巊梡丄俠俹倀俠俴俷俠俲傪僔僗僥儉僋儘僢僋乮栺俁丏俆俈俋俵俫倸乯偲偟偰巊梡偟傑偡

丂

俹俽俧

倁俢俹偼俿俬惢俿俵俽俋俋侾俉俙傪巊梡丄俠俹倀俠俴俷俠俲傪僔僗僥儉僋儘僢僋乮栺俁丏俆俈俋俵俫倸乯偲偟偰巊梡偟傑偡

丂

俹俽俧

俽俶俈俇係俉俋俙俶傪巊梡丄僋儘僢僋偼俁丏俈俆俋俵俫倸偱丄俵俽俛偼俢侽丄俴俽俛偼俢俈偵宷偑偭偰偄傑偡

乛倂俤偲俼俤俙俢倄怣崋偑繫偑偭偰偄傑偡

乛倂俙俬俿偼俼俆乮係丏俈倠乯偺僾儖傾僢僾偵側偭偰俠俹倀偺乛倂俙俬俿偵繫偑偭偰偄傑偡

丂

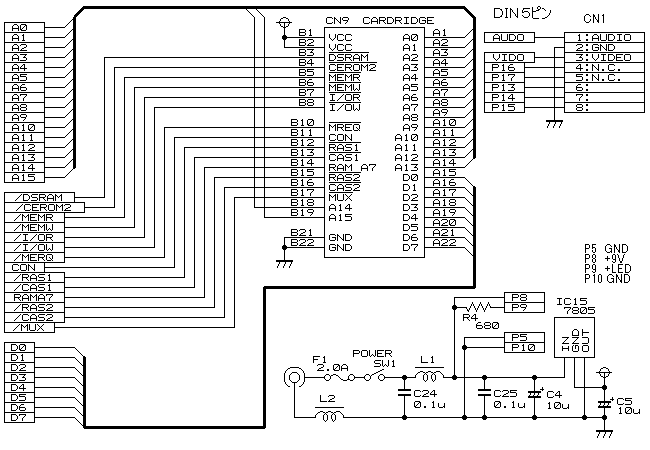

俼俷俵

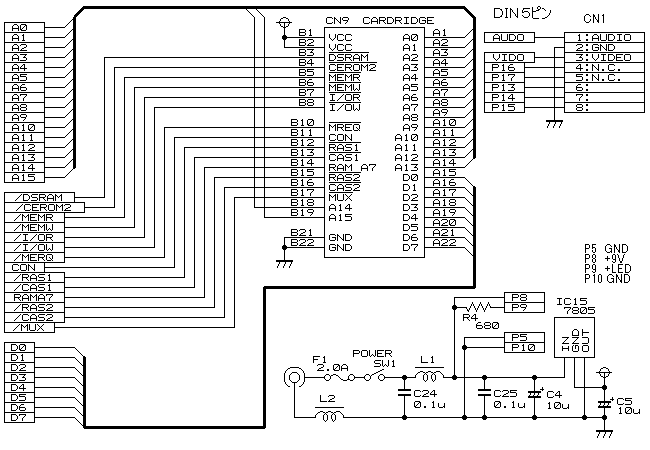

俼俷俵偼杮懱偵偼撪憼偝傟偰偍傜偢丄僇乕僩儕僢僕枖偼僇乕僪乮梫僇乕僪僉儍僢僠儍乕乯偱嫙媼偡傞宍偲側傝傑偡

儊僈俼俷俵偼僇乕僩儕僢僕撪偺儅僢僷乕偱惂屼偝傟傑偡乮儘儗僢僞偺徰憸乯

丂

俼俙俵

俼俙俵偼杮懱偵俀俲俛乮侽俠侽侽侽俫亅侽俠俈俥俥俫乯

僇乕僩儕僢僕乮俛俁抂巕傪忢偵侾乯偐傜杮懱撪俼俙俵傪巊梡嬛巭偵偡傞偙偲偑弌棃傑偡

偙傟偵傛傝怴偨偵捛壛偱偒傞傛偆偵愝寁偝傟偰偄傑偡

僇乕僩儕僢僕抂巕偐傜偼俢亅俼俙俵偺僐儞僩儘乕儖怣崋偑弌偰偄傞偺偱俢亅俼俙俵丄俽亅俼俙俵偺儊儌儕憹愝偑壜擻

丂

僇乕僩儕僢僕抂巕

俽俶俈俇係俉俋俙俶傪巊梡丄僋儘僢僋偼俁丏俈俆俋俵俫倸偱丄俵俽俛偼俢侽丄俴俽俛偼俢俈偵宷偑偭偰偄傑偡

乛倂俤偲俼俤俙俢倄怣崋偑繫偑偭偰偄傑偡

乛倂俙俬俿偼俼俆乮係丏俈倠乯偺僾儖傾僢僾偵側偭偰俠俹倀偺乛倂俙俬俿偵繫偑偭偰偄傑偡

丂

俼俷俵

俼俷俵偼杮懱偵偼撪憼偝傟偰偍傜偢丄僇乕僩儕僢僕枖偼僇乕僪乮梫僇乕僪僉儍僢僠儍乕乯偱嫙媼偡傞宍偲側傝傑偡

儊僈俼俷俵偼僇乕僩儕僢僕撪偺儅僢僷乕偱惂屼偝傟傑偡乮儘儗僢僞偺徰憸乯

丂

俼俙俵

俼俙俵偼杮懱偵俀俲俛乮侽俠侽侽侽俫亅侽俠俈俥俥俫乯

僇乕僩儕僢僕乮俛俁抂巕傪忢偵侾乯偐傜杮懱撪俼俙俵傪巊梡嬛巭偵偡傞偙偲偑弌棃傑偡

偙傟偵傛傝怴偨偵捛壛偱偒傞傛偆偵愝寁偝傟偰偄傑偡

僇乕僩儕僢僕抂巕偐傜偼俢亅俼俙俵偺僐儞僩儘乕儖怣崋偑弌偰偄傞偺偱俢亅俼俙俵丄俽亅俼俙俵偺儊儌儕憹愝偑壜擻

丂

僇乕僩儕僢僕抂巕

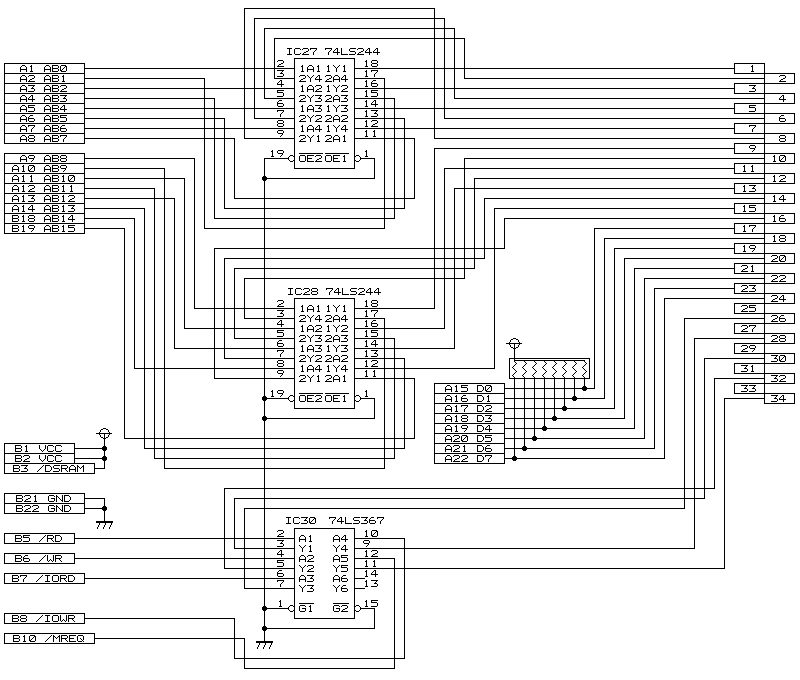

丂丂俛俈偺乛俬乛俷俼丄俛俉偺乛俬乛俷俼偼億乕僩侽俠侽俫亅侽俥俥俫

丂

俬乛俷億乕僩

丂丂俛俈偺乛俬乛俷俼丄俛俉偺乛俬乛俷俼偼億乕僩侽俠侽俫亅侽俥俥俫

丂

俬乛俷億乕僩

丂侽侽侽俫亅侽俁俥俫丗枹巊梡

丂侽係侽俫亅侽俈俥俫丗俹俽俧丂丂丂俽俶俈俇係俉俋丂丄億乕僩侽俈俥俫丂丂丂丂丂傪巊梡

丂侽俉侽俫亅侽俛俥俫丗倁俢俹丂丂丂俿俵俽俋俋侾俉俙丄億乕僩侽俛俤俫亅侽俛俥俫傪巊梡

丂侽俠侽俫亅侽俢俥俫丗僉乕儃乕僪亄俰俷倄抂巕丂丂丂丄億乕僩侽俢俠俫亅侽俢俥俫傪巊梡

丂侽俤侽俫亅侽俥俥俫丗奼挘梡丂丂丂俽俥亅俈侽侽侽

丂

億乕僩侽俈俥俫

丂俹俽俧丂俽俶俈俇係俉俋偺億乕僩偱偡丅

丂

億乕僩侽俛俤俫亅侽俛俥俫

丂倁俢俹丂俿俵俽俋俋侾俉俙偺億乕僩偱偡丅

丂

僉乕儃乕僪丄俰俷倄僷僢僪抂巕丄僇僙僢僩抂巕丄僔儕傾儖僾儕儞僞抂巕

丂億乕僩侽俢俠俫丗俹俙丂僉乕僨乕僞

丂丂倓俈丗俲俤倄丂俹俙俈丂乮擖椡乯

丂丂倓俇丗俲俤倄丂俹俙俇丂乮擖椡乯

丂丂倓俆丗俲俤倄丂俹俙俆丂乮擖椡乯

丂丂倓係丗俲俤倄丂俹俙係丂乮擖椡乯

丂丂倓俁丗俲俤倄丂俹俙俁丂乮擖椡乯

丂丂倓俀丗俲俤倄丂俹俙俀丂乮擖椡乯

丂丂倓侾丗俲俤倄丂俹俙侾丂乮擖椡乯

丂丂倓侽丗俲俤倄丂俹俙侽丂乮擖椡乯

丂

丂億乕僩侽俢俢俫丗俹俛丂僉乕僨乕僞丄俠俵俿丄僔儕傾儖僾儕儞僞丄僇乕僩儕僢僕抂巕

丂丂倓俈丗俠俵俿丂俴俷俙俢丂丂丂乮擖椡乯

丂丂倓俇丗俽俹俼丂俛倀俽倄丂丂丂乮擖椡乯

丂丂倓俆丗俽俹俼丂乛俥俙倀俴俿丂乮擖椡乯

丂丂倓係丗俤倃俿丂乛俠俷俶俿丂丂乮擖椡乯

丂丂倓俁丗俲俤倄丂俹俛俁丂丂丂丂乮擖椡乯

丂丂倓俀丗俲俤倄丂俹俛俀丂丂丂丂乮擖椡乯

丂丂倓侾丗俲俤倄丂俹俛侾丂丂丂丂乮擖椡乯

丂丂倓侽丗俲俤倄丂俹俛侽丂丂丂丂乮擖椡乯

丂

丂億乕僩侽俢俤俫丗俹俠丂僉乕僙儗僋僩丄俠俵俿丄僔儕傾儖僾儕儞僞

丂丂倓俈丗俽俹俼丂乛俥俤俤俢丂丂乮弌椡乯

丂丂倓俇丗俽俹俼丂乛俼俤俽俤俿丂乮弌椡乯

丂丂倓俆丗俽俹俼丂俢俙俿俙丂丂丂乮弌椡乯

丂丂倓係丗俠俵俿丂俽俙倁俤丂丂丂乮弌椡乯

丂丂倓俁丗俠俵俿丂俵俷俿俷俼丂丂乮弌椡乯侾亖俷値丄侽亖俷倖倖乮枹幚憰乯

丂丂倓俀丗俲俤倄丂俽俤俴丂俹俀丂乮弌椡乯

丂丂倓侾丗俲俤倄丂俽俤俴丂俹侾丂乮弌椡乯

丂丂倓侽丗俲俤倄丂俽俤俴丂俹侽丂乮弌椡乯

丂

丂億乕僩侽俢俥俫丗俉俀俆俆偺俠倂

丂

俽俥亅俈侽侽侽梡乮俽俠亅俁侽侽侽愱梡奼挘儐僯僢僩乯億乕僩

丂俁僀儞僠丂僐儞僷僋僩丒僼儘僢僺乕乮俠俥乯僪儔僀僽侾戜憰旛乮儀儖僩僪儔僀僽嬱摦乯

丂儊儌儕傪俼俙俵俇係俲俛(俢亅俼俙俵俇係俲俛乯丄俬俹俴 俼俷俵係俲俛

丂俼俽亅俀俁俀俠乮儃乕儗乕僩偼杮懱撪偺僕儍儞僷乕偱愝掕壜擻偩偑僴儞僟晅偗偱屌掕偝傟偄傞乯

丂僙儞僩僯僋僗巇條偺僾儕儞僞抂巕傪憰旛

丂偨偩偟奼挘抂巕偼柍偟

丂俽俠亅俁侽侽侽偺妱傝崬傒偼慡偰巊梡偟偰偄傞堊俥俢俠妱傝崬傒偼巊梡偱偒傑偣傫

丂偟偨偑偭偰俥俢俠偺乛俬俶俿傪億乕僩儕儞僌偡傞巇條偵側偭偰偄傑偡丅

丂

俥俢俠兪俢俈俇俆俙俠偺億乕僩

丂侽俤侽俫丗僗僥乕僞僗儗僕僗僞

丂侽俤侾俫丗僨乕僞儗僕僗僞

丂

俹俹俬丂兪俢俉俀俆俆俙俠亅俀偺億乕僩

丂侽俤係俫丗俹俙

丂丂倓俈丗丂亅

丂丂倓俇丗丂亅

丂丂倓俆丗丂亅

丂丂倓係丗丂亅

丂丂倓俁丗丂亅

丂丂倓俀丗俥俢俢丂俬俶俢俤倃

丂丂倓侾丗俹俼俿丂俛倀俽倄

丂丂倓侽丗俥俢俢丂俥俢俠俬俶俿

丂

丂侽俤俆俫丗俹俛

丂丂倓俈丗俹俼俿丂俢俛俈

丂丂倓俇丗俹俼俿丂俢俛俇

丂丂倓俆丗俹俼俿丂俢俛俆

丂丂倓係丗俹俼俿丂俢俛係

丂丂倓俁丗俹俼俿丂俢俛俁

丂丂倓俀丗俹俼俿丂俢俛俀

丂丂倓侾丗俹俼俿丂俢俛侾

丂丂倓侽丗俹俼俿丂俢俛侽

丂

丂侽俤俇俫丗俹俠

丂丂倓俈丗俹俼俿丂乛俽俿俼俷俛俤

丂丂倓俇丗俽倄俽丂乛俼俷俵丂俽俤俴丂丂侾亖俼俙俵傪慖戰丂丄侽亖俬俹俴丂俼俷俵傪慖戰

丂丂倓俆丗俥俢俢丂丠丠丠晄柧丂丂丂丂丂侾亖僪儔僀僽偺婲摦丄侽亖僪儔僀僽偺掆巭

丂丂倓係丗丂亅

丂丂倓俁丗俥俢俢丂俼俤俽俤俿丂丂丂丂丂侾亖儕僙僢僩偡傞丄侽亖儕僙僢僩偟側偄

丂丂倓俀丗俥俢俢丂俿俠

丂丂倓侾丗俥俢俢丂乛俵俷俿俷俼丂俷俶丂侾亖儌乕僞乕僆僼丄侽亖儌乕僞乕僆儞

丂丂倓侽丗俥俢俢丂乛俬俶倀俽俤

丂

丂侽俤俈俫丗俉俀俆俆偺俠倂

丂侽侽侽俫亅侽俁俥俫丗枹巊梡

丂侽係侽俫亅侽俈俥俫丗俹俽俧丂丂丂俽俶俈俇係俉俋丂丄億乕僩侽俈俥俫丂丂丂丂丂傪巊梡

丂侽俉侽俫亅侽俛俥俫丗倁俢俹丂丂丂俿俵俽俋俋侾俉俙丄億乕僩侽俛俤俫亅侽俛俥俫傪巊梡

丂侽俠侽俫亅侽俢俥俫丗僉乕儃乕僪亄俰俷倄抂巕丂丂丂丄億乕僩侽俢俠俫亅侽俢俥俫傪巊梡

丂侽俤侽俫亅侽俥俥俫丗奼挘梡丂丂丂俽俥亅俈侽侽侽

丂

億乕僩侽俈俥俫

丂俹俽俧丂俽俶俈俇係俉俋偺億乕僩偱偡丅

丂

億乕僩侽俛俤俫亅侽俛俥俫

丂倁俢俹丂俿俵俽俋俋侾俉俙偺億乕僩偱偡丅

丂

僉乕儃乕僪丄俰俷倄僷僢僪抂巕丄僇僙僢僩抂巕丄僔儕傾儖僾儕儞僞抂巕

丂億乕僩侽俢俠俫丗俹俙丂僉乕僨乕僞

丂丂倓俈丗俲俤倄丂俹俙俈丂乮擖椡乯

丂丂倓俇丗俲俤倄丂俹俙俇丂乮擖椡乯

丂丂倓俆丗俲俤倄丂俹俙俆丂乮擖椡乯

丂丂倓係丗俲俤倄丂俹俙係丂乮擖椡乯

丂丂倓俁丗俲俤倄丂俹俙俁丂乮擖椡乯

丂丂倓俀丗俲俤倄丂俹俙俀丂乮擖椡乯

丂丂倓侾丗俲俤倄丂俹俙侾丂乮擖椡乯

丂丂倓侽丗俲俤倄丂俹俙侽丂乮擖椡乯

丂

丂億乕僩侽俢俢俫丗俹俛丂僉乕僨乕僞丄俠俵俿丄僔儕傾儖僾儕儞僞丄僇乕僩儕僢僕抂巕

丂丂倓俈丗俠俵俿丂俴俷俙俢丂丂丂乮擖椡乯

丂丂倓俇丗俽俹俼丂俛倀俽倄丂丂丂乮擖椡乯

丂丂倓俆丗俽俹俼丂乛俥俙倀俴俿丂乮擖椡乯

丂丂倓係丗俤倃俿丂乛俠俷俶俿丂丂乮擖椡乯

丂丂倓俁丗俲俤倄丂俹俛俁丂丂丂丂乮擖椡乯

丂丂倓俀丗俲俤倄丂俹俛俀丂丂丂丂乮擖椡乯

丂丂倓侾丗俲俤倄丂俹俛侾丂丂丂丂乮擖椡乯

丂丂倓侽丗俲俤倄丂俹俛侽丂丂丂丂乮擖椡乯

丂

丂億乕僩侽俢俤俫丗俹俠丂僉乕僙儗僋僩丄俠俵俿丄僔儕傾儖僾儕儞僞

丂丂倓俈丗俽俹俼丂乛俥俤俤俢丂丂乮弌椡乯

丂丂倓俇丗俽俹俼丂乛俼俤俽俤俿丂乮弌椡乯

丂丂倓俆丗俽俹俼丂俢俙俿俙丂丂丂乮弌椡乯

丂丂倓係丗俠俵俿丂俽俙倁俤丂丂丂乮弌椡乯

丂丂倓俁丗俠俵俿丂俵俷俿俷俼丂丂乮弌椡乯侾亖俷値丄侽亖俷倖倖乮枹幚憰乯

丂丂倓俀丗俲俤倄丂俽俤俴丂俹俀丂乮弌椡乯

丂丂倓侾丗俲俤倄丂俽俤俴丂俹侾丂乮弌椡乯

丂丂倓侽丗俲俤倄丂俽俤俴丂俹侽丂乮弌椡乯

丂

丂億乕僩侽俢俥俫丗俉俀俆俆偺俠倂

丂

俽俥亅俈侽侽侽梡乮俽俠亅俁侽侽侽愱梡奼挘儐僯僢僩乯億乕僩

丂俁僀儞僠丂僐儞僷僋僩丒僼儘僢僺乕乮俠俥乯僪儔僀僽侾戜憰旛乮儀儖僩僪儔僀僽嬱摦乯

丂儊儌儕傪俼俙俵俇係俲俛(俢亅俼俙俵俇係俲俛乯丄俬俹俴 俼俷俵係俲俛

丂俼俽亅俀俁俀俠乮儃乕儗乕僩偼杮懱撪偺僕儍儞僷乕偱愝掕壜擻偩偑僴儞僟晅偗偱屌掕偝傟偄傞乯

丂僙儞僩僯僋僗巇條偺僾儕儞僞抂巕傪憰旛

丂偨偩偟奼挘抂巕偼柍偟

丂俽俠亅俁侽侽侽偺妱傝崬傒偼慡偰巊梡偟偰偄傞堊俥俢俠妱傝崬傒偼巊梡偱偒傑偣傫

丂偟偨偑偭偰俥俢俠偺乛俬俶俿傪億乕僩儕儞僌偡傞巇條偵側偭偰偄傑偡丅

丂

俥俢俠兪俢俈俇俆俙俠偺億乕僩

丂侽俤侽俫丗僗僥乕僞僗儗僕僗僞

丂侽俤侾俫丗僨乕僞儗僕僗僞

丂

俹俹俬丂兪俢俉俀俆俆俙俠亅俀偺億乕僩

丂侽俤係俫丗俹俙

丂丂倓俈丗丂亅

丂丂倓俇丗丂亅

丂丂倓俆丗丂亅

丂丂倓係丗丂亅

丂丂倓俁丗丂亅

丂丂倓俀丗俥俢俢丂俬俶俢俤倃

丂丂倓侾丗俹俼俿丂俛倀俽倄

丂丂倓侽丗俥俢俢丂俥俢俠俬俶俿

丂

丂侽俤俆俫丗俹俛

丂丂倓俈丗俹俼俿丂俢俛俈

丂丂倓俇丗俹俼俿丂俢俛俇

丂丂倓俆丗俹俼俿丂俢俛俆

丂丂倓係丗俹俼俿丂俢俛係

丂丂倓俁丗俹俼俿丂俢俛俁

丂丂倓俀丗俹俼俿丂俢俛俀

丂丂倓侾丗俹俼俿丂俢俛侾

丂丂倓侽丗俹俼俿丂俢俛侽

丂

丂侽俤俇俫丗俹俠

丂丂倓俈丗俹俼俿丂乛俽俿俼俷俛俤

丂丂倓俇丗俽倄俽丂乛俼俷俵丂俽俤俴丂丂侾亖俼俙俵傪慖戰丂丄侽亖俬俹俴丂俼俷俵傪慖戰

丂丂倓俆丗俥俢俢丂丠丠丠晄柧丂丂丂丂丂侾亖僪儔僀僽偺婲摦丄侽亖僪儔僀僽偺掆巭

丂丂倓係丗丂亅

丂丂倓俁丗俥俢俢丂俼俤俽俤俿丂丂丂丂丂侾亖儕僙僢僩偡傞丄侽亖儕僙僢僩偟側偄

丂丂倓俀丗俥俢俢丂俿俠

丂丂倓侾丗俥俢俢丂乛俵俷俿俷俼丂俷俶丂侾亖儌乕僞乕僆僼丄侽亖儌乕僞乕僆儞

丂丂倓侽丗俥俢俢丂乛俬俶倀俽俤

丂

丂侽俤俈俫丗俉俀俆俆偺俠倂

丂

俼俽亅俀俁俀俠乮兪俢俉俀俆侾俙俥俠乯偺億乕僩

丂侽俤俉俫丗僨乕僞儗僕僗僞

丂侽俤俋俫丗僐儞僩儘乕儖儗僕僗僞

丂

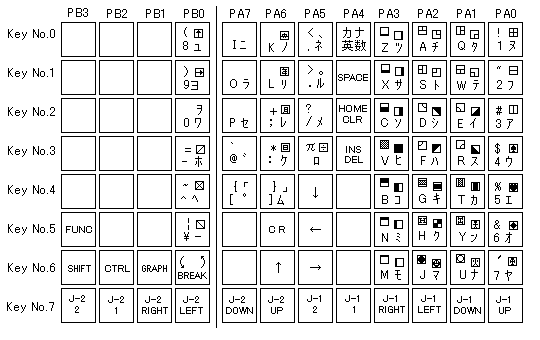

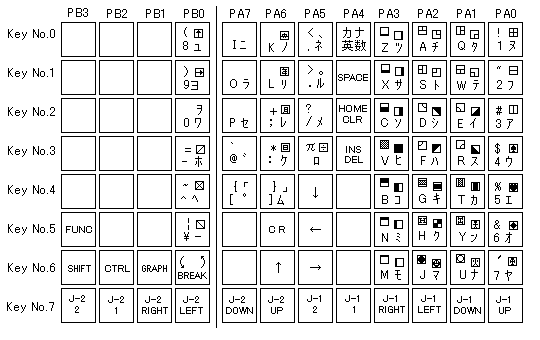

僉乕儅僩儕僋僗

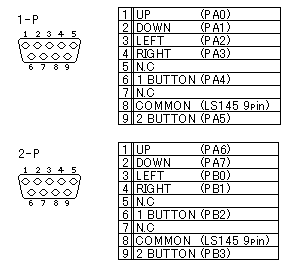

丂俽俠亅俁侽侽侽偼俽俧亅侾侽侽侽丄俽俤俧俙丂俵俙俼俲丂III偲堘偄

丂慡偰俉俀俆俆偺億乕僩偱擖弌椡傪峴偄傑偡

丂偦偟偰丄俲倕倷丂俶倧俈傪慖戰偟偨応崌偵俰俷倄抂巕侾偲俀偺俉僺儞乮懠婡庬偱偼俧俶俢乯偑乭侽乭偵側傝

丂俰俷倄僨乕僞偼僉乕儃乕僪偲摨偠偔俹俙俈亅侽丄俹俛俁亅侽偺撉傒崬傒偑弌棃傞傛偆偵側傝傑偡

丂亄俆倁偲俧俶俢偑柍偄堊丄楢幩僷僢僪偼巊梡弌棃傑偣傫

丂曽岦偲儃僞儞侾偲儃僞儞俀偼侾亖僆僼丄侽亖僆儞

丂

丂俽俠亅俁侽侽侽偼俽俧亅侾侽侽侽丄俽俤俧俙丂俵俙俼俲丂III偲堘偄

丂慡偰俉俀俆俆偺億乕僩偱擖弌椡傪峴偄傑偡

丂偦偟偰丄俲倕倷丂俶倧俈傪慖戰偟偨応崌偵俰俷倄抂巕侾偲俀偺俉僺儞乮懠婡庬偱偼俧俶俢乯偑乭侽乭偵側傝

丂俰俷倄僨乕僞偼僉乕儃乕僪偲摨偠偔俹俙俈亅侽丄俹俛俁亅侽偺撉傒崬傒偑弌棃傞傛偆偵側傝傑偡

丂亄俆倁偲俧俶俢偑柍偄堊丄楢幩僷僢僪偼巊梡弌棃傑偣傫

丂曽岦偲儃僞儞侾偲儃僞儞俀偼侾亖僆僼丄侽亖僆儞

丂

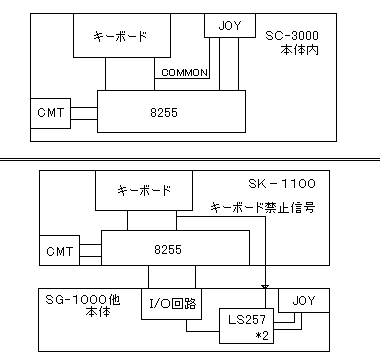

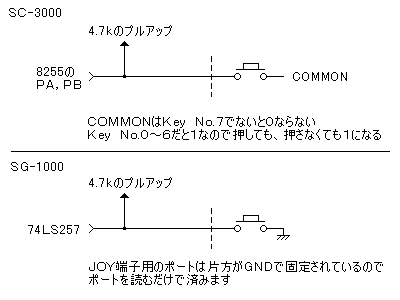

懠婡庬乮俽俧亅侾侽侽侽摍乯偲偺堘偄

丂  丂僷僜僐儞偲偟偰愝寁偝傟偰偄傞偺偱俢-俼俙俵偺儕僼儗僢僔儏夞楬偑偁傝僇乕僩儕僢僕抂巕偵弌椡偟偰偄傑偡丅

丂俰俷倄抂巕偑俉俀俆俆偺億乕僩偱撉傫偱偄偰倁俠俠偑弌偰側偔俧俶俢傕側偔俴俽侾係俆偺僙儗僋僞偱

丂俰俷倄抂巕傪僙儗僋僩偡傞偲侽乮俠俷俵俵俷俶乯偵偟偰偄傞

丂懠婡庬亄俽俲亅侾侾侽侽偱偼僉乕儃乕僪傪撉傓帪偼俰俷倄抂巕嬛巭偵側偭偰僉乕僨乕僞傪撉傒

丂俰俷倄抂巕傪撉傓帪偼僉乕儃乕僪傪嬛巭偵側偭偰杮懱撪偺俰俷倄抂巕偺僨乕僞傪撉傒傑偡

丂

丂僉乕儃乕僪亄俰俷倄抂巕偲俰俷倄抂巕偺傒偺俀庬椶偑偁傞堊

丂椉曽偺懳墳偡傞堊偵偼僉乕儃乕僪偑愙懕偝傟偰偄傞偐僠僃僢僋傪峴偄

丂俰俷倄抂巕偺傒偲僉乕儃乕僪晅偒偺俀偮儖乕僠儞傪帩偮昁梫偑偁傝傑偡

丂俽俠亅俁侽侽侽偱偼僉乕儃乕僪亄俰俷倄抂巕偺儖乕僠儞偑巊梡偝傟傑偡

丂

丂僷僜僐儞偲偟偰愝寁偝傟偰偄傞偺偱俢-俼俙俵偺儕僼儗僢僔儏夞楬偑偁傝僇乕僩儕僢僕抂巕偵弌椡偟偰偄傑偡丅

丂俰俷倄抂巕偑俉俀俆俆偺億乕僩偱撉傫偱偄偰倁俠俠偑弌偰側偔俧俶俢傕側偔俴俽侾係俆偺僙儗僋僞偱

丂俰俷倄抂巕傪僙儗僋僩偡傞偲侽乮俠俷俵俵俷俶乯偵偟偰偄傞

丂懠婡庬亄俽俲亅侾侾侽侽偱偼僉乕儃乕僪傪撉傓帪偼俰俷倄抂巕嬛巭偵側偭偰僉乕僨乕僞傪撉傒

丂俰俷倄抂巕傪撉傓帪偼僉乕儃乕僪傪嬛巭偵側偭偰杮懱撪偺俰俷倄抂巕偺僨乕僞傪撉傒傑偡

丂

丂僉乕儃乕僪亄俰俷倄抂巕偲俰俷倄抂巕偺傒偺俀庬椶偑偁傞堊

丂椉曽偺懳墳偡傞堊偵偼僉乕儃乕僪偑愙懕偝傟偰偄傞偐僠僃僢僋傪峴偄

丂俰俷倄抂巕偺傒偲僉乕儃乕僪晅偒偺俀偮儖乕僠儞傪帩偮昁梫偑偁傝傑偡

丂俽俠亅俁侽侽侽偱偼僉乕儃乕僪亄俰俷倄抂巕偺儖乕僠儞偑巊梡偝傟傑偡

丂  丂僉乕儃乕僪堦懱宆側偺偱僉乕儃乕僪憖嶌偡傞偲怳摦偱杮懱偲僇僙僢僩偺愙怗晄椙偵側傝傗偡偔朶憱偟傗偡偄丅

丂朶憱傪杊偖堊偵巻傪愜偭偰杮懱偲僇乕僩儕僢僕偺寗娫偵媗傔傞摍偺岺晇傪偟側偄偲埨怱偟偰巊偆帠偑弌棃傑偣傫丅

丂

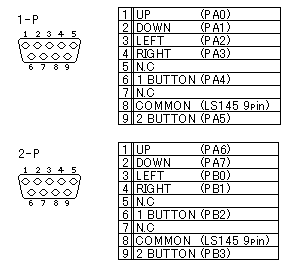

丂俰俷倄抂巕

丂丂俽俠亅俁侽侽侽偺応崌

丂丂丂俹俹俬惂屼丂曽岦丄僩儕僈乕儃僞儞偼擖弌椡偑壜擻

丂

丂丂俽俧亅侾侽侽侽丄俵俙俼俲丂俬俬俬偺応崌

丂丂丂俴俽俀俆俈惂屼丂曽岦丄僩儕僈乕儃僞儞偼擖椡偺傒

丂

丂丂儅僗僞乕僔僗僥儉偺応崌

丂丂丂僇僗僞儉僠僢僾惂屼丂曽岦偼擖椡偺傒丄僩儕僈乕儃僞儞偼擖弌椡偑壜擻

丂

丂僉乕儃乕僪堦懱宆側偺偱僉乕儃乕僪憖嶌偡傞偲怳摦偱杮懱偲僇僙僢僩偺愙怗晄椙偵側傝傗偡偔朶憱偟傗偡偄丅

丂朶憱傪杊偖堊偵巻傪愜偭偰杮懱偲僇乕僩儕僢僕偺寗娫偵媗傔傞摍偺岺晇傪偟側偄偲埨怱偟偰巊偆帠偑弌棃傑偣傫丅

丂

丂俰俷倄抂巕

丂丂俽俠亅俁侽侽侽偺応崌

丂丂丂俹俹俬惂屼丂曽岦丄僩儕僈乕儃僞儞偼擖弌椡偑壜擻

丂

丂丂俽俧亅侾侽侽侽丄俵俙俼俲丂俬俬俬偺応崌

丂丂丂俴俽俀俆俈惂屼丂曽岦丄僩儕僈乕儃僞儞偼擖椡偺傒

丂

丂丂儅僗僞乕僔僗僥儉偺応崌

丂丂丂僇僗僞儉僠僢僾惂屼丂曽岦偼擖椡偺傒丄僩儕僈乕儃僞儞偼擖弌椡偑壜擻

丂

杮懱偺嬻偒僷僞乕儞

丂屻婜儘僢僩偼倁俢俹嬤偔偵俿俿俴丂俬俠摍偑嵹傞僷僞乕儞偑偁傝傑偡乮侾俈侾亅俆侽係俉乯

丂奀奜偺俹俙俴巇條偺俽俠亅俁侽侽侽偱巊傢傟傞僔僗僥儉僋儘僢僋梡偺僷僞乕儞偱俴俽侽係偑嵹傝傑偡

丂俿俵俽俋俋俀俉傗俿俵俽俋俋俀俋偱偼僔僗僥儉梡俁丏俆俈俋俵俫倸偺僋儘僢僋怣崋偑弌側偄偨傔

丂倁俢俹梡偲偼暿偵僔僗僥儉僋儘僢僋乮俠俹倀丄俹俽俧梡乯偑昁梫偵側傝傑偡丅

丂偦偙偱怴偟偄儘僢僩偱偼擔杮乮俶俿俽俠乯巇條偲俹俙俴巇條偲摨偠儊僀儞婎斅偵偟偰

丂彮側偄曄峏偱懳墳偡傞傛偆偵側偭偰偄傑偡丅乮俹俙俴巇條偼僒僽婎斅偱價僨僆夞楬傪帩偭偰偄傑偡乯

丂

丂傑偨丄倁俢俹傪俿俵俽俋俋俀俉偵曄偊偰僔僗僥儉僋儘僢僋夞楬傪庢傝偮偗偰

丂婎斅拞墰偺僔僗僥儉僋儘僢僋偺僕儍儞僷傪庢傝乮僒僽婎斅傪偲傝偮偗傞僗儁乕僒偺寠傪傑偨偄偱偄傞僕儍儞僷乯

丂婎斅偵婰偝傟偰偄傞僔僗僥儉僋儘僢僋偵僕儍儞僷傪捛壛

丂倁俢俹偺怓嵎偐傜儅僩儕僢僋僗夞楬傪惢嶌偟偰傗傟偽傾僫儘僌俼俧俛弌椡偑弌棃傞偼偢偱偡丅

丂傑偨價僨僆抂巕偺僷僞乕儞傕俼俧俛抂巕僐僱僋僞偵曄偊傜傟傞傛偆偵側偭偰偄傑偡丅

丂

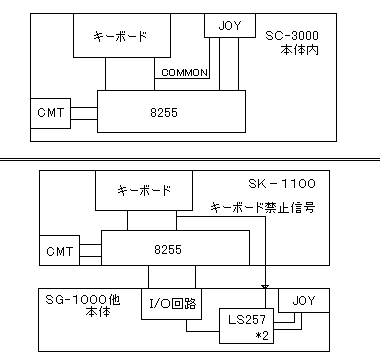

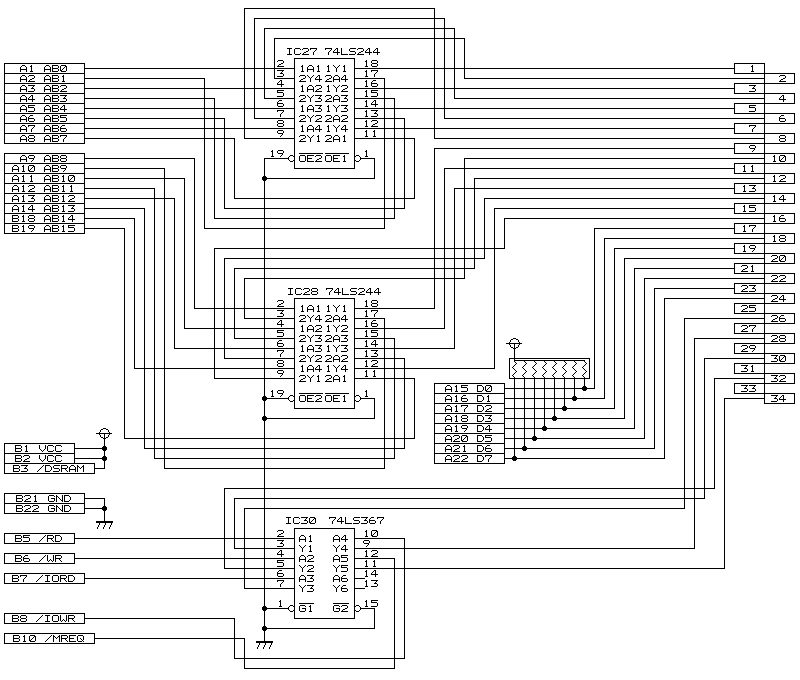

俽俥亅俈侽侽侽僇乕僩儕僢僕晹暘偺夞楬恾

俽俥亅俈侽侽侽杮懱偲宷偖堊偺僶僗僶僢僼傽偱偡丅

杮懱乮俽俥亅俈侽侽侽乯偺俼俙俵偼僙儖僼儕僼儗僢僔儏俢亅俼俙俵丂俵俶係俀俇係仏俉傪巊梡偟偰偄傞偺偱僇乕僩儕僢僕偺儕僼儗僢僔儏偼晄梫丅

丂

俽俥亅俈侽侽侽杮懱偲宷偖堊偺僶僗僶僢僼傽偱偡丅

杮懱乮俽俥亅俈侽侽侽乯偺俼俙俵偼僙儖僼儕僼儗僢僔儏俢亅俼俙俵丂俵俶係俀俇係仏俉傪巊梡偟偰偄傞偺偱僇乕僩儕僢僕偺儕僼儗僢僔儏偼晄梫丅

丂

Home 傊栠傞

俠俹倀偼俶俤俠偺俹俢俈俉侽亅侾傪巊梡丂僋儘僢僋偼栺俁丏俆俈俋俵俫倸

妱傝崬傒偼儌乕僪侾偱俶俵俬偼俼俤俽俤俿僉乕乮億乕僘僉乕乯丄俬俶俿偼倁俢俹偐傜偺倁俽倄俶俠偵妱傝摉偰傜傟偰偄傑偡

乛俷俽俼俙俵偼杮懱撪偺俽俼俙俵偺乛俠俽偵宷偑偭偰偄偰侾偵偡傞帠偵傛偭偰巊梡嬛巭偵弌棃傑偡

丂

倁俢俹

俠俹倀偼俶俤俠偺俹俢俈俉侽亅侾傪巊梡丂僋儘僢僋偼栺俁丏俆俈俋俵俫倸

妱傝崬傒偼儌乕僪侾偱俶俵俬偼俼俤俽俤俿僉乕乮億乕僘僉乕乯丄俬俶俿偼倁俢俹偐傜偺倁俽倄俶俠偵妱傝摉偰傜傟偰偄傑偡

乛俷俽俼俙俵偼杮懱撪偺俽俼俙俵偺乛俠俽偵宷偑偭偰偄偰侾偵偡傞帠偵傛偭偰巊梡嬛巭偵弌棃傑偡

丂

倁俢俹

倁俢俹偼俿俬惢俿俵俽俋俋侾俉俙傪巊梡丄俠俹倀俠俴俷俠俲傪僔僗僥儉僋儘僢僋乮栺俁丏俆俈俋俵俫倸乯偲偟偰巊梡偟傑偡

丂

俹俽俧

倁俢俹偼俿俬惢俿俵俽俋俋侾俉俙傪巊梡丄俠俹倀俠俴俷俠俲傪僔僗僥儉僋儘僢僋乮栺俁丏俆俈俋俵俫倸乯偲偟偰巊梡偟傑偡

丂

俹俽俧

俽俶俈俇係俉俋俙俶傪巊梡丄僋儘僢僋偼俁丏俈俆俋俵俫倸偱丄俵俽俛偼俢侽丄俴俽俛偼俢俈偵宷偑偭偰偄傑偡

乛倂俤偲俼俤俙俢倄怣崋偑繫偑偭偰偄傑偡

乛倂俙俬俿偼俼俆乮係丏俈倠乯偺僾儖傾僢僾偵側偭偰俠俹倀偺乛倂俙俬俿偵繫偑偭偰偄傑偡

丂

俼俷俵

俼俷俵偼杮懱偵偼撪憼偝傟偰偍傜偢丄僇乕僩儕僢僕枖偼僇乕僪乮梫僇乕僪僉儍僢僠儍乕乯偱嫙媼偡傞宍偲側傝傑偡

儊僈俼俷俵偼僇乕僩儕僢僕撪偺儅僢僷乕偱惂屼偝傟傑偡乮儘儗僢僞偺徰憸乯

丂

俼俙俵

俼俙俵偼杮懱偵俀俲俛乮侽俠侽侽侽俫亅侽俠俈俥俥俫乯

僇乕僩儕僢僕乮俛俁抂巕傪忢偵侾乯偐傜杮懱撪俼俙俵傪巊梡嬛巭偵偡傞偙偲偑弌棃傑偡

偙傟偵傛傝怴偨偵捛壛偱偒傞傛偆偵愝寁偝傟偰偄傑偡

僇乕僩儕僢僕抂巕偐傜偼俢亅俼俙俵偺僐儞僩儘乕儖怣崋偑弌偰偄傞偺偱俢亅俼俙俵丄俽亅俼俙俵偺儊儌儕憹愝偑壜擻

丂

僇乕僩儕僢僕抂巕

俽俶俈俇係俉俋俙俶傪巊梡丄僋儘僢僋偼俁丏俈俆俋俵俫倸偱丄俵俽俛偼俢侽丄俴俽俛偼俢俈偵宷偑偭偰偄傑偡

乛倂俤偲俼俤俙俢倄怣崋偑繫偑偭偰偄傑偡

乛倂俙俬俿偼俼俆乮係丏俈倠乯偺僾儖傾僢僾偵側偭偰俠俹倀偺乛倂俙俬俿偵繫偑偭偰偄傑偡

丂

俼俷俵

俼俷俵偼杮懱偵偼撪憼偝傟偰偍傜偢丄僇乕僩儕僢僕枖偼僇乕僪乮梫僇乕僪僉儍僢僠儍乕乯偱嫙媼偡傞宍偲側傝傑偡

儊僈俼俷俵偼僇乕僩儕僢僕撪偺儅僢僷乕偱惂屼偝傟傑偡乮儘儗僢僞偺徰憸乯

丂

俼俙俵

俼俙俵偼杮懱偵俀俲俛乮侽俠侽侽侽俫亅侽俠俈俥俥俫乯

僇乕僩儕僢僕乮俛俁抂巕傪忢偵侾乯偐傜杮懱撪俼俙俵傪巊梡嬛巭偵偡傞偙偲偑弌棃傑偡

偙傟偵傛傝怴偨偵捛壛偱偒傞傛偆偵愝寁偝傟偰偄傑偡

僇乕僩儕僢僕抂巕偐傜偼俢亅俼俙俵偺僐儞僩儘乕儖怣崋偑弌偰偄傞偺偱俢亅俼俙俵丄俽亅俼俙俵偺儊儌儕憹愝偑壜擻

丂

僇乕僩儕僢僕抂巕

丂丂俛俈偺乛俬乛俷俼丄俛俉偺乛俬乛俷俼偼億乕僩侽俠侽俫亅侽俥俥俫

丂

俬乛俷億乕僩

丂丂俛俈偺乛俬乛俷俼丄俛俉偺乛俬乛俷俼偼億乕僩侽俠侽俫亅侽俥俥俫

丂

俬乛俷億乕僩

丂侽侽侽俫亅侽俁俥俫丗枹巊梡

丂侽係侽俫亅侽俈俥俫丗俹俽俧丂丂丂俽俶俈俇係俉俋丂丄億乕僩侽俈俥俫丂丂丂丂丂傪巊梡

丂侽俉侽俫亅侽俛俥俫丗倁俢俹丂丂丂俿俵俽俋俋侾俉俙丄億乕僩侽俛俤俫亅侽俛俥俫傪巊梡

丂侽俠侽俫亅侽俢俥俫丗僉乕儃乕僪亄俰俷倄抂巕丂丂丂丄億乕僩侽俢俠俫亅侽俢俥俫傪巊梡

丂侽俤侽俫亅侽俥俥俫丗奼挘梡丂丂丂俽俥亅俈侽侽侽

丂

億乕僩侽俈俥俫

丂俹俽俧丂俽俶俈俇係俉俋偺億乕僩偱偡丅

丂

億乕僩侽俛俤俫亅侽俛俥俫

丂倁俢俹丂俿俵俽俋俋侾俉俙偺億乕僩偱偡丅

丂

僉乕儃乕僪丄俰俷倄僷僢僪抂巕丄僇僙僢僩抂巕丄僔儕傾儖僾儕儞僞抂巕

丂億乕僩侽俢俠俫丗俹俙丂僉乕僨乕僞

丂丂倓俈丗俲俤倄丂俹俙俈丂乮擖椡乯

丂丂倓俇丗俲俤倄丂俹俙俇丂乮擖椡乯

丂丂倓俆丗俲俤倄丂俹俙俆丂乮擖椡乯

丂丂倓係丗俲俤倄丂俹俙係丂乮擖椡乯

丂丂倓俁丗俲俤倄丂俹俙俁丂乮擖椡乯

丂丂倓俀丗俲俤倄丂俹俙俀丂乮擖椡乯

丂丂倓侾丗俲俤倄丂俹俙侾丂乮擖椡乯

丂丂倓侽丗俲俤倄丂俹俙侽丂乮擖椡乯

丂

丂億乕僩侽俢俢俫丗俹俛丂僉乕僨乕僞丄俠俵俿丄僔儕傾儖僾儕儞僞丄僇乕僩儕僢僕抂巕

丂丂倓俈丗俠俵俿丂俴俷俙俢丂丂丂乮擖椡乯

丂丂倓俇丗俽俹俼丂俛倀俽倄丂丂丂乮擖椡乯

丂丂倓俆丗俽俹俼丂乛俥俙倀俴俿丂乮擖椡乯

丂丂倓係丗俤倃俿丂乛俠俷俶俿丂丂乮擖椡乯

丂丂倓俁丗俲俤倄丂俹俛俁丂丂丂丂乮擖椡乯

丂丂倓俀丗俲俤倄丂俹俛俀丂丂丂丂乮擖椡乯

丂丂倓侾丗俲俤倄丂俹俛侾丂丂丂丂乮擖椡乯

丂丂倓侽丗俲俤倄丂俹俛侽丂丂丂丂乮擖椡乯

丂

丂億乕僩侽俢俤俫丗俹俠丂僉乕僙儗僋僩丄俠俵俿丄僔儕傾儖僾儕儞僞

丂丂倓俈丗俽俹俼丂乛俥俤俤俢丂丂乮弌椡乯

丂丂倓俇丗俽俹俼丂乛俼俤俽俤俿丂乮弌椡乯

丂丂倓俆丗俽俹俼丂俢俙俿俙丂丂丂乮弌椡乯

丂丂倓係丗俠俵俿丂俽俙倁俤丂丂丂乮弌椡乯

丂丂倓俁丗俠俵俿丂俵俷俿俷俼丂丂乮弌椡乯侾亖俷値丄侽亖俷倖倖乮枹幚憰乯

丂丂倓俀丗俲俤倄丂俽俤俴丂俹俀丂乮弌椡乯

丂丂倓侾丗俲俤倄丂俽俤俴丂俹侾丂乮弌椡乯

丂丂倓侽丗俲俤倄丂俽俤俴丂俹侽丂乮弌椡乯

丂

丂億乕僩侽俢俥俫丗俉俀俆俆偺俠倂

丂

俽俥亅俈侽侽侽梡乮俽俠亅俁侽侽侽愱梡奼挘儐僯僢僩乯億乕僩

丂俁僀儞僠丂僐儞僷僋僩丒僼儘僢僺乕乮俠俥乯僪儔僀僽侾戜憰旛乮儀儖僩僪儔僀僽嬱摦乯

丂儊儌儕傪俼俙俵俇係俲俛(俢亅俼俙俵俇係俲俛乯丄俬俹俴 俼俷俵係俲俛

丂俼俽亅俀俁俀俠乮儃乕儗乕僩偼杮懱撪偺僕儍儞僷乕偱愝掕壜擻偩偑僴儞僟晅偗偱屌掕偝傟偄傞乯

丂僙儞僩僯僋僗巇條偺僾儕儞僞抂巕傪憰旛

丂偨偩偟奼挘抂巕偼柍偟

丂俽俠亅俁侽侽侽偺妱傝崬傒偼慡偰巊梡偟偰偄傞堊俥俢俠妱傝崬傒偼巊梡偱偒傑偣傫

丂偟偨偑偭偰俥俢俠偺乛俬俶俿傪億乕僩儕儞僌偡傞巇條偵側偭偰偄傑偡丅

丂

俥俢俠兪俢俈俇俆俙俠偺億乕僩

丂侽俤侽俫丗僗僥乕僞僗儗僕僗僞

丂侽俤侾俫丗僨乕僞儗僕僗僞

丂

俹俹俬丂兪俢俉俀俆俆俙俠亅俀偺億乕僩

丂侽俤係俫丗俹俙

丂丂倓俈丗丂亅

丂丂倓俇丗丂亅

丂丂倓俆丗丂亅

丂丂倓係丗丂亅

丂丂倓俁丗丂亅

丂丂倓俀丗俥俢俢丂俬俶俢俤倃

丂丂倓侾丗俹俼俿丂俛倀俽倄

丂丂倓侽丗俥俢俢丂俥俢俠俬俶俿

丂

丂侽俤俆俫丗俹俛

丂丂倓俈丗俹俼俿丂俢俛俈

丂丂倓俇丗俹俼俿丂俢俛俇

丂丂倓俆丗俹俼俿丂俢俛俆

丂丂倓係丗俹俼俿丂俢俛係

丂丂倓俁丗俹俼俿丂俢俛俁

丂丂倓俀丗俹俼俿丂俢俛俀

丂丂倓侾丗俹俼俿丂俢俛侾

丂丂倓侽丗俹俼俿丂俢俛侽

丂

丂侽俤俇俫丗俹俠

丂丂倓俈丗俹俼俿丂乛俽俿俼俷俛俤

丂丂倓俇丗俽倄俽丂乛俼俷俵丂俽俤俴丂丂侾亖俼俙俵傪慖戰丂丄侽亖俬俹俴丂俼俷俵傪慖戰

丂丂倓俆丗俥俢俢丂丠丠丠晄柧丂丂丂丂丂侾亖僪儔僀僽偺婲摦丄侽亖僪儔僀僽偺掆巭

丂丂倓係丗丂亅

丂丂倓俁丗俥俢俢丂俼俤俽俤俿丂丂丂丂丂侾亖儕僙僢僩偡傞丄侽亖儕僙僢僩偟側偄

丂丂倓俀丗俥俢俢丂俿俠

丂丂倓侾丗俥俢俢丂乛俵俷俿俷俼丂俷俶丂侾亖儌乕僞乕僆僼丄侽亖儌乕僞乕僆儞

丂丂倓侽丗俥俢俢丂乛俬俶倀俽俤

丂

丂侽俤俈俫丗俉俀俆俆偺俠倂

丂侽侽侽俫亅侽俁俥俫丗枹巊梡

丂侽係侽俫亅侽俈俥俫丗俹俽俧丂丂丂俽俶俈俇係俉俋丂丄億乕僩侽俈俥俫丂丂丂丂丂傪巊梡

丂侽俉侽俫亅侽俛俥俫丗倁俢俹丂丂丂俿俵俽俋俋侾俉俙丄億乕僩侽俛俤俫亅侽俛俥俫傪巊梡

丂侽俠侽俫亅侽俢俥俫丗僉乕儃乕僪亄俰俷倄抂巕丂丂丂丄億乕僩侽俢俠俫亅侽俢俥俫傪巊梡

丂侽俤侽俫亅侽俥俥俫丗奼挘梡丂丂丂俽俥亅俈侽侽侽

丂

億乕僩侽俈俥俫

丂俹俽俧丂俽俶俈俇係俉俋偺億乕僩偱偡丅

丂

億乕僩侽俛俤俫亅侽俛俥俫

丂倁俢俹丂俿俵俽俋俋侾俉俙偺億乕僩偱偡丅

丂

僉乕儃乕僪丄俰俷倄僷僢僪抂巕丄僇僙僢僩抂巕丄僔儕傾儖僾儕儞僞抂巕

丂億乕僩侽俢俠俫丗俹俙丂僉乕僨乕僞

丂丂倓俈丗俲俤倄丂俹俙俈丂乮擖椡乯

丂丂倓俇丗俲俤倄丂俹俙俇丂乮擖椡乯

丂丂倓俆丗俲俤倄丂俹俙俆丂乮擖椡乯

丂丂倓係丗俲俤倄丂俹俙係丂乮擖椡乯

丂丂倓俁丗俲俤倄丂俹俙俁丂乮擖椡乯

丂丂倓俀丗俲俤倄丂俹俙俀丂乮擖椡乯

丂丂倓侾丗俲俤倄丂俹俙侾丂乮擖椡乯

丂丂倓侽丗俲俤倄丂俹俙侽丂乮擖椡乯

丂

丂億乕僩侽俢俢俫丗俹俛丂僉乕僨乕僞丄俠俵俿丄僔儕傾儖僾儕儞僞丄僇乕僩儕僢僕抂巕

丂丂倓俈丗俠俵俿丂俴俷俙俢丂丂丂乮擖椡乯

丂丂倓俇丗俽俹俼丂俛倀俽倄丂丂丂乮擖椡乯

丂丂倓俆丗俽俹俼丂乛俥俙倀俴俿丂乮擖椡乯

丂丂倓係丗俤倃俿丂乛俠俷俶俿丂丂乮擖椡乯

丂丂倓俁丗俲俤倄丂俹俛俁丂丂丂丂乮擖椡乯

丂丂倓俀丗俲俤倄丂俹俛俀丂丂丂丂乮擖椡乯

丂丂倓侾丗俲俤倄丂俹俛侾丂丂丂丂乮擖椡乯

丂丂倓侽丗俲俤倄丂俹俛侽丂丂丂丂乮擖椡乯

丂

丂億乕僩侽俢俤俫丗俹俠丂僉乕僙儗僋僩丄俠俵俿丄僔儕傾儖僾儕儞僞

丂丂倓俈丗俽俹俼丂乛俥俤俤俢丂丂乮弌椡乯

丂丂倓俇丗俽俹俼丂乛俼俤俽俤俿丂乮弌椡乯

丂丂倓俆丗俽俹俼丂俢俙俿俙丂丂丂乮弌椡乯

丂丂倓係丗俠俵俿丂俽俙倁俤丂丂丂乮弌椡乯

丂丂倓俁丗俠俵俿丂俵俷俿俷俼丂丂乮弌椡乯侾亖俷値丄侽亖俷倖倖乮枹幚憰乯

丂丂倓俀丗俲俤倄丂俽俤俴丂俹俀丂乮弌椡乯

丂丂倓侾丗俲俤倄丂俽俤俴丂俹侾丂乮弌椡乯

丂丂倓侽丗俲俤倄丂俽俤俴丂俹侽丂乮弌椡乯

丂

丂億乕僩侽俢俥俫丗俉俀俆俆偺俠倂

丂

俽俥亅俈侽侽侽梡乮俽俠亅俁侽侽侽愱梡奼挘儐僯僢僩乯億乕僩

丂俁僀儞僠丂僐儞僷僋僩丒僼儘僢僺乕乮俠俥乯僪儔僀僽侾戜憰旛乮儀儖僩僪儔僀僽嬱摦乯

丂儊儌儕傪俼俙俵俇係俲俛(俢亅俼俙俵俇係俲俛乯丄俬俹俴 俼俷俵係俲俛

丂俼俽亅俀俁俀俠乮儃乕儗乕僩偼杮懱撪偺僕儍儞僷乕偱愝掕壜擻偩偑僴儞僟晅偗偱屌掕偝傟偄傞乯

丂僙儞僩僯僋僗巇條偺僾儕儞僞抂巕傪憰旛

丂偨偩偟奼挘抂巕偼柍偟

丂俽俠亅俁侽侽侽偺妱傝崬傒偼慡偰巊梡偟偰偄傞堊俥俢俠妱傝崬傒偼巊梡偱偒傑偣傫

丂偟偨偑偭偰俥俢俠偺乛俬俶俿傪億乕僩儕儞僌偡傞巇條偵側偭偰偄傑偡丅

丂

俥俢俠兪俢俈俇俆俙俠偺億乕僩

丂侽俤侽俫丗僗僥乕僞僗儗僕僗僞

丂侽俤侾俫丗僨乕僞儗僕僗僞

丂

俹俹俬丂兪俢俉俀俆俆俙俠亅俀偺億乕僩

丂侽俤係俫丗俹俙

丂丂倓俈丗丂亅

丂丂倓俇丗丂亅

丂丂倓俆丗丂亅

丂丂倓係丗丂亅

丂丂倓俁丗丂亅

丂丂倓俀丗俥俢俢丂俬俶俢俤倃

丂丂倓侾丗俹俼俿丂俛倀俽倄

丂丂倓侽丗俥俢俢丂俥俢俠俬俶俿

丂

丂侽俤俆俫丗俹俛

丂丂倓俈丗俹俼俿丂俢俛俈

丂丂倓俇丗俹俼俿丂俢俛俇

丂丂倓俆丗俹俼俿丂俢俛俆

丂丂倓係丗俹俼俿丂俢俛係

丂丂倓俁丗俹俼俿丂俢俛俁

丂丂倓俀丗俹俼俿丂俢俛俀

丂丂倓侾丗俹俼俿丂俢俛侾

丂丂倓侽丗俹俼俿丂俢俛侽

丂

丂侽俤俇俫丗俹俠

丂丂倓俈丗俹俼俿丂乛俽俿俼俷俛俤

丂丂倓俇丗俽倄俽丂乛俼俷俵丂俽俤俴丂丂侾亖俼俙俵傪慖戰丂丄侽亖俬俹俴丂俼俷俵傪慖戰

丂丂倓俆丗俥俢俢丂丠丠丠晄柧丂丂丂丂丂侾亖僪儔僀僽偺婲摦丄侽亖僪儔僀僽偺掆巭

丂丂倓係丗丂亅

丂丂倓俁丗俥俢俢丂俼俤俽俤俿丂丂丂丂丂侾亖儕僙僢僩偡傞丄侽亖儕僙僢僩偟側偄

丂丂倓俀丗俥俢俢丂俿俠

丂丂倓侾丗俥俢俢丂乛俵俷俿俷俼丂俷俶丂侾亖儌乕僞乕僆僼丄侽亖儌乕僞乕僆儞

丂丂倓侽丗俥俢俢丂乛俬俶倀俽俤

丂

丂侽俤俈俫丗俉俀俆俆偺俠倂

丂俽俠亅俁侽侽侽偼俽俧亅侾侽侽侽丄俽俤俧俙丂俵俙俼俲丂III偲堘偄

丂慡偰俉俀俆俆偺億乕僩偱擖弌椡傪峴偄傑偡

丂偦偟偰丄俲倕倷丂俶倧俈傪慖戰偟偨応崌偵俰俷倄抂巕侾偲俀偺俉僺儞乮懠婡庬偱偼俧俶俢乯偑乭侽乭偵側傝

丂俰俷倄僨乕僞偼僉乕儃乕僪偲摨偠偔俹俙俈亅侽丄俹俛俁亅侽偺撉傒崬傒偑弌棃傞傛偆偵側傝傑偡

丂亄俆倁偲俧俶俢偑柍偄堊丄楢幩僷僢僪偼巊梡弌棃傑偣傫

丂曽岦偲儃僞儞侾偲儃僞儞俀偼侾亖僆僼丄侽亖僆儞

丂

丂俽俠亅俁侽侽侽偼俽俧亅侾侽侽侽丄俽俤俧俙丂俵俙俼俲丂III偲堘偄

丂慡偰俉俀俆俆偺億乕僩偱擖弌椡傪峴偄傑偡

丂偦偟偰丄俲倕倷丂俶倧俈傪慖戰偟偨応崌偵俰俷倄抂巕侾偲俀偺俉僺儞乮懠婡庬偱偼俧俶俢乯偑乭侽乭偵側傝

丂俰俷倄僨乕僞偼僉乕儃乕僪偲摨偠偔俹俙俈亅侽丄俹俛俁亅侽偺撉傒崬傒偑弌棃傞傛偆偵側傝傑偡

丂亄俆倁偲俧俶俢偑柍偄堊丄楢幩僷僢僪偼巊梡弌棃傑偣傫

丂曽岦偲儃僞儞侾偲儃僞儞俀偼侾亖僆僼丄侽亖僆儞

丂

丂僷僜僐儞偲偟偰愝寁偝傟偰偄傞偺偱俢-俼俙俵偺儕僼儗僢僔儏夞楬偑偁傝僇乕僩儕僢僕抂巕偵弌椡偟偰偄傑偡丅

丂俰俷倄抂巕偑俉俀俆俆偺億乕僩偱撉傫偱偄偰倁俠俠偑弌偰側偔俧俶俢傕側偔俴俽侾係俆偺僙儗僋僞偱

丂俰俷倄抂巕傪僙儗僋僩偡傞偲侽乮俠俷俵俵俷俶乯偵偟偰偄傞

丂懠婡庬亄俽俲亅侾侾侽侽偱偼僉乕儃乕僪傪撉傓帪偼俰俷倄抂巕嬛巭偵側偭偰僉乕僨乕僞傪撉傒

丂俰俷倄抂巕傪撉傓帪偼僉乕儃乕僪傪嬛巭偵側偭偰杮懱撪偺俰俷倄抂巕偺僨乕僞傪撉傒傑偡

丂

丂僉乕儃乕僪亄俰俷倄抂巕偲俰俷倄抂巕偺傒偺俀庬椶偑偁傞堊

丂椉曽偺懳墳偡傞堊偵偼僉乕儃乕僪偑愙懕偝傟偰偄傞偐僠僃僢僋傪峴偄

丂俰俷倄抂巕偺傒偲僉乕儃乕僪晅偒偺俀偮儖乕僠儞傪帩偮昁梫偑偁傝傑偡

丂俽俠亅俁侽侽侽偱偼僉乕儃乕僪亄俰俷倄抂巕偺儖乕僠儞偑巊梡偝傟傑偡

丂

丂僷僜僐儞偲偟偰愝寁偝傟偰偄傞偺偱俢-俼俙俵偺儕僼儗僢僔儏夞楬偑偁傝僇乕僩儕僢僕抂巕偵弌椡偟偰偄傑偡丅

丂俰俷倄抂巕偑俉俀俆俆偺億乕僩偱撉傫偱偄偰倁俠俠偑弌偰側偔俧俶俢傕側偔俴俽侾係俆偺僙儗僋僞偱

丂俰俷倄抂巕傪僙儗僋僩偡傞偲侽乮俠俷俵俵俷俶乯偵偟偰偄傞

丂懠婡庬亄俽俲亅侾侾侽侽偱偼僉乕儃乕僪傪撉傓帪偼俰俷倄抂巕嬛巭偵側偭偰僉乕僨乕僞傪撉傒

丂俰俷倄抂巕傪撉傓帪偼僉乕儃乕僪傪嬛巭偵側偭偰杮懱撪偺俰俷倄抂巕偺僨乕僞傪撉傒傑偡

丂

丂僉乕儃乕僪亄俰俷倄抂巕偲俰俷倄抂巕偺傒偺俀庬椶偑偁傞堊

丂椉曽偺懳墳偡傞堊偵偼僉乕儃乕僪偑愙懕偝傟偰偄傞偐僠僃僢僋傪峴偄

丂俰俷倄抂巕偺傒偲僉乕儃乕僪晅偒偺俀偮儖乕僠儞傪帩偮昁梫偑偁傝傑偡

丂俽俠亅俁侽侽侽偱偼僉乕儃乕僪亄俰俷倄抂巕偺儖乕僠儞偑巊梡偝傟傑偡

丂  丂僉乕儃乕僪堦懱宆側偺偱僉乕儃乕僪憖嶌偡傞偲怳摦偱杮懱偲僇僙僢僩偺愙怗晄椙偵側傝傗偡偔朶憱偟傗偡偄丅

丂朶憱傪杊偖堊偵巻傪愜偭偰杮懱偲僇乕僩儕僢僕偺寗娫偵媗傔傞摍偺岺晇傪偟側偄偲埨怱偟偰巊偆帠偑弌棃傑偣傫丅

丂

丂俰俷倄抂巕

丂丂俽俠亅俁侽侽侽偺応崌

丂丂丂俹俹俬惂屼丂曽岦丄僩儕僈乕儃僞儞偼擖弌椡偑壜擻

丂

丂丂俽俧亅侾侽侽侽丄俵俙俼俲丂俬俬俬偺応崌

丂丂丂俴俽俀俆俈惂屼丂曽岦丄僩儕僈乕儃僞儞偼擖椡偺傒

丂

丂丂儅僗僞乕僔僗僥儉偺応崌

丂丂丂僇僗僞儉僠僢僾惂屼丂曽岦偼擖椡偺傒丄僩儕僈乕儃僞儞偼擖弌椡偑壜擻

丂

丂僉乕儃乕僪堦懱宆側偺偱僉乕儃乕僪憖嶌偡傞偲怳摦偱杮懱偲僇僙僢僩偺愙怗晄椙偵側傝傗偡偔朶憱偟傗偡偄丅

丂朶憱傪杊偖堊偵巻傪愜偭偰杮懱偲僇乕僩儕僢僕偺寗娫偵媗傔傞摍偺岺晇傪偟側偄偲埨怱偟偰巊偆帠偑弌棃傑偣傫丅

丂

丂俰俷倄抂巕

丂丂俽俠亅俁侽侽侽偺応崌

丂丂丂俹俹俬惂屼丂曽岦丄僩儕僈乕儃僞儞偼擖弌椡偑壜擻

丂

丂丂俽俧亅侾侽侽侽丄俵俙俼俲丂俬俬俬偺応崌

丂丂丂俴俽俀俆俈惂屼丂曽岦丄僩儕僈乕儃僞儞偼擖椡偺傒

丂

丂丂儅僗僞乕僔僗僥儉偺応崌

丂丂丂僇僗僞儉僠僢僾惂屼丂曽岦偼擖椡偺傒丄僩儕僈乕儃僞儞偼擖弌椡偑壜擻

丂

俽俥亅俈侽侽侽杮懱偲宷偖堊偺僶僗僶僢僼傽偱偡丅

杮懱乮俽俥亅俈侽侽侽乯偺俼俙俵偼僙儖僼儕僼儗僢僔儏俢亅俼俙俵丂俵俶係俀俇係仏俉傪巊梡偟偰偄傞偺偱僇乕僩儕僢僕偺儕僼儗僢僔儏偼晄梫丅

丂

俽俥亅俈侽侽侽杮懱偲宷偖堊偺僶僗僶僢僼傽偱偡丅

杮懱乮俽俥亅俈侽侽侽乯偺俼俙俵偼僙儖僼儕僼儗僢僔儏俢亅俼俙俵丂俵俶係俀俇係仏俉傪巊梡偟偰偄傞偺偱僇乕僩儕僢僕偺儕僼儗僢僔儏偼晄梫丅

丂