CreatiVision丂乮僋儕僄僀僩價僕儑儞乯乮拲乯夞楬恾偼嶲峫掱搙偵偟偰壓偝偄丅

CreatiVision偺僗儁僢僋

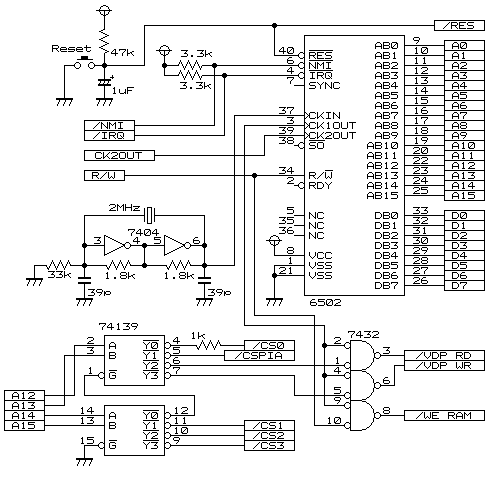

| MPU | 6502 2MHz |

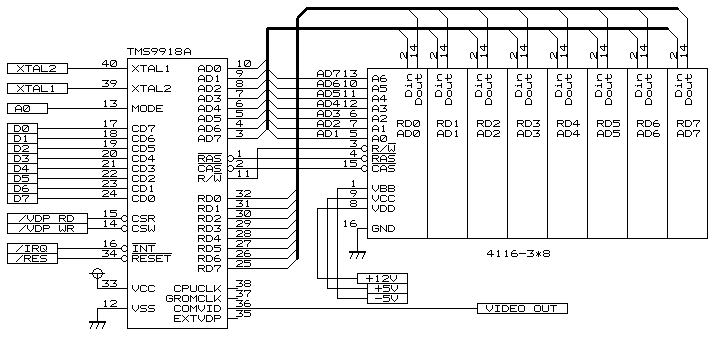

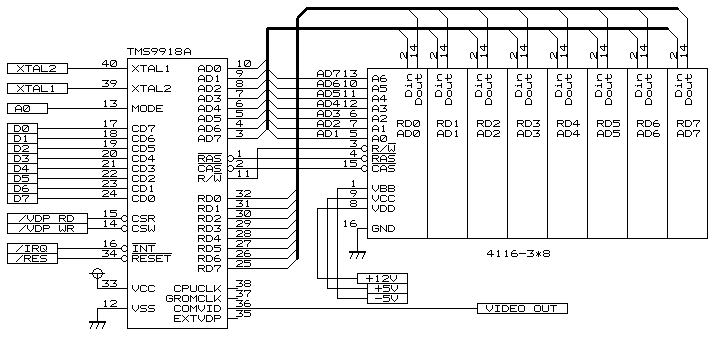

| VDP | TMS9918A |

| PSG | SN76489 |

| ROM | 2KB乮奼挘壜乯 |

| RAM | 1KB乮奼挘壜乯 |

| V-RAM | 16KB |

丂

俇俆侽俀傪巊偭偨僎乕儉僷僜僐儞丄僉乕儃乕僪偑廲恀拞偱俀偮偵暘偐傟丄

偦傟偑僎乕儉梡僷僢僪偵側傞

僆僾僔儑儞偺俛俙俽俬俠丂倁倕倰侾丏侽偼

摉帪偺僋儔僗偺儅僔儞乮俽俠亅俁侽侽侽丄傄傘偆懢丄俵俆摍乯偵斾妑偵側傜側偄

抶偝偲抣抜偺崅偝傪屩傞

乮偮偄偱偵杮懱偺婎斅偺偮偔傝偺崜偝傕僗僑僀傕偺偺僲僀僘懳嶔偼偟偭偐傝偟偰偄傞乯

僔乕儖僪偑僴儞僟偯偗偱屌掕偝傟偰偄傞偺偱儊儞僥僫儞僗惈偼僛儘丄

偲偙傠偳偙傠偵僷僞乕儞僇僢僩傗僕儍儞僷偑偁傝

懡彮偺巇條曄峏偑偁偭偨柾條

杮懱僷僢働乕僕偵偼僗僋儕乕儞僗僐傾昞帵丄暆峀偄僶儕僄乕僔儑儞丄慛柧偱鉱枾側俿倁夋柺丄

僔儏儈儗僀僔儑儞僒僂儞僪

偲傛偔暘偐傜側偄帠偑彂偐傟偰偄傞偺傕垽沢乮僔儏儈儗僀僔儑儞丠乯

傑偨丄僇僞儘僌偺俛俙俽俬俠偼倁倕倰侾亅侾偵側偭偰偄傞偲偙傠傪傒傞偲

俀偮偺僶乕僕儑儞偑懚嵼偡傞丠

僴乕僪帺懱偼僔儞僾儖偱奼挘傕偦傟側傝偵梡堄偝傟偰偄傞

丂

丂

俵俹倀廃傝

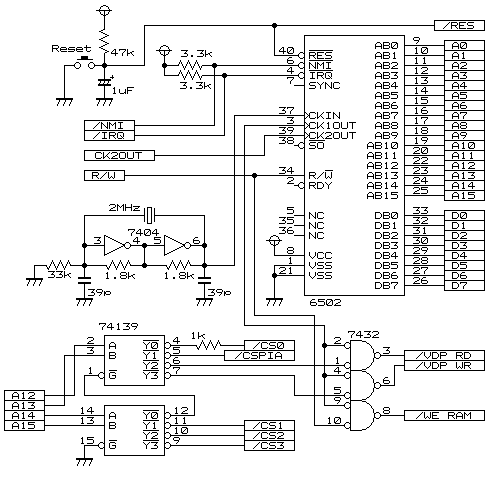

俵俹倀偼俇俆侽俀丂僋儘僢僋偼俀俵俫倸

俛俬俷俽偼僇乕僩儕僢僕偺抂巕傪僔儑乕僩偟偰巊梡嫋壜偟偰偄傑偡丅

丂乛俠俽侽亖亹侽仏仏仏

丂乛俠俽侾亖亹係仏仏仏

丂乛俠俽俀亖亹俉仏仏仏

丂乛俠俽俁亖亹俠仏仏仏

丂

丂

儊儌儕

俵俹倀偼俇俆侽俀丂僋儘僢僋偼俀俵俫倸

俛俬俷俽偼僇乕僩儕僢僕偺抂巕傪僔儑乕僩偟偰巊梡嫋壜偟偰偄傑偡丅

丂乛俠俽侽亖亹侽仏仏仏

丂乛俠俽侾亖亹係仏仏仏

丂乛俠俽俀亖亹俉仏仏仏

丂乛俠俽俁亖亹俠仏仏仏

丂

丂

儊儌儕

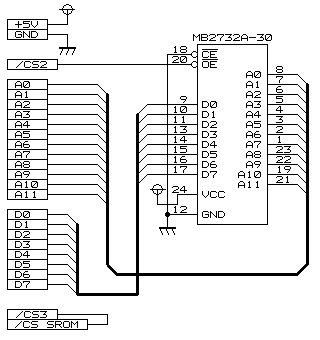

杮懱撪偵偼俀俲俛偺儅僗僋俼俷俵乮俛俬俷俽乯偲

侾俲仏係俛倝倲偺俽俼俙俵偑俀偮撪憼偝傟偰偄傑偡

俛俬俷俽偼愗傝棧偡帠傕壜擻偱偡丅

俿俵俵俁俁係俹丗俠俼俠亖們俁們俆俋侽們俇

丂

丂

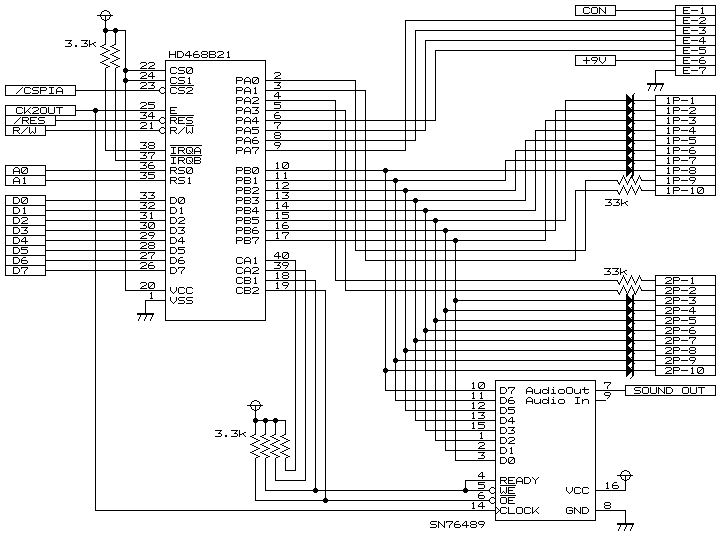

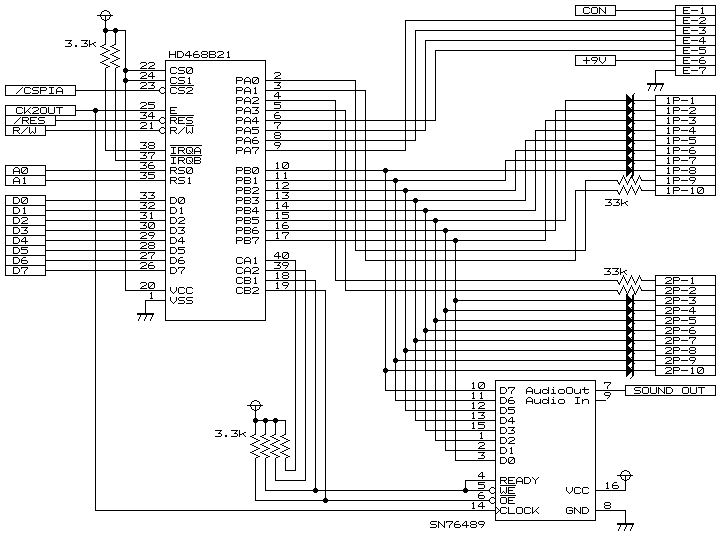

俹俬俙丂俫俢係俇俉俛俀侾

杮懱撪偵偼俀俲俛偺儅僗僋俼俷俵乮俛俬俷俽乯偲

侾俲仏係俛倝倲偺俽俼俙俵偑俀偮撪憼偝傟偰偄傑偡

俛俬俷俽偼愗傝棧偡帠傕壜擻偱偡丅

俿俵俵俁俁係俹丗俠俼俠亖們俁們俆俋侽們俇

丂

丂

俹俬俙丂俫俢係俇俉俛俀侾

僉乕儃乕僪丄俹俽俧丄奼挘抂巕偼俹俬俙偱惂屼偝傟傑偡

俹俙偱僉乕儃乕僪乮僐儞僩儘乕儔乯丄奼挘抂巕偺慖戰丄

俠俛偱俹俽俧偺慖戰丄俹俛偑僨乕僞偺弌椡

奼挘抂巕偼俠俵俿偑宷偑傝傑偡

丂俤亅俀丂俹俙俈丂俼俤俙俢乛倂俼俬俿俤

丂俤亅係丂俹俙俆丂丠丠丠俼俤俵俷俿俤

丂俤亅俆丂俹俙係丂丠丠丠俼俤俵俷俿俤

丂

倁俢俹丂俿俵俽俋俋侾俉俙

僉乕儃乕僪丄俹俽俧丄奼挘抂巕偼俹俬俙偱惂屼偝傟傑偡

俹俙偱僉乕儃乕僪乮僐儞僩儘乕儔乯丄奼挘抂巕偺慖戰丄

俠俛偱俹俽俧偺慖戰丄俹俛偑僨乕僞偺弌椡

奼挘抂巕偼俠俵俿偑宷偑傝傑偡

丂俤亅俀丂俹俙俈丂俼俤俙俢乛倂俼俬俿俤

丂俤亅係丂俹俙俆丂丠丠丠俼俤俵俷俿俤

丂俤亅俆丂俹俙係丂丠丠丠俼俤俵俷俿俤

丂

倁俢俹丂俿俵俽俋俋侾俉俙

崱夞僋儘僢僋夞楬偼徣偄偰偄傑偡偑10.738俵俫倸偱偡

倁俽倄俶俠妱傝崬傒偼俬俼俻偵側傝傑偡

丂

丂

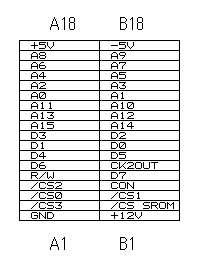

僐僱僋僞

崱夞僋儘僢僋夞楬偼徣偄偰偄傑偡偑10.738俵俫倸偱偡

倁俽倄俶俠妱傝崬傒偼俬俼俻偵側傝傑偡

丂

丂

僐僱僋僞

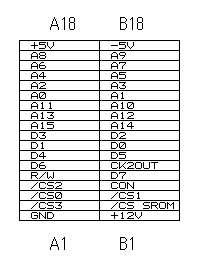

僇乕僩儕僢僕僐僱僋僞偱偡

俙1偑嵍忋偵側傝俛侾俉偑塃壓偵側傝傑偡

捠忢偺僎乕儉偩偲俛俬俷俽傕巊梡偡傞堊

乛俠俽俁偲乛俠俽丂俽俼俷俵偑僔儑乕僩偝傟傑偡

乛俠俽 侽偑弌偰偄傞偺偱夞楬偵傛偭偰偼

儊儌儕傗俬乛俷億乕僩偲偲偟偰巊梡壜擻偱偡

俠俲俀俷倀俿偼俀俵俫倸偱偡

丂

僎乕儉僇僙僢僩

僇乕僩儕僢僕僐僱僋僞偱偡

俙1偑嵍忋偵側傝俛侾俉偑塃壓偵側傝傑偡

捠忢偺僎乕儉偩偲俛俬俷俽傕巊梡偡傞堊

乛俠俽俁偲乛俠俽丂俽俼俷俵偑僔儑乕僩偝傟傑偡

乛俠俽 侽偑弌偰偄傞偺偱夞楬偵傛偭偰偼

儊儌儕傗俬乛俷億乕僩偲偲偟偰巊梡壜擻偱偡

俠俲俀俷倀俿偼俀俵俫倸偱偡

丂

僎乕儉僇僙僢僩

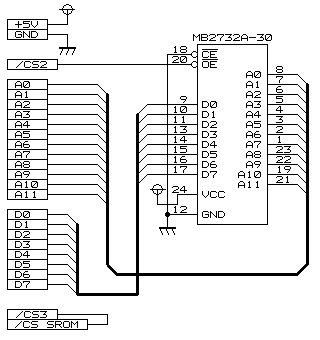

僋儗乕僕僠僉儞偺俼俷俵僇僙僢僩偱偡

婎斅偼傕偆堦偮俼俷俵偑嵹偣傜傟傞條偵愝寁偝傟偰偄傑偡

乛俠俽俁偲乛俠俽 俽俼俷俵偑僔儑乕僩偟偰偄傞偺偱

杮懱撪偺俛俬俷俽傪巊梡偟偰偄傑偡

俛俬俷俽偼僇乕僩儕僢僕偺桳柍栤傢偢

亹俛俥俥俠偵僕儍儞僾偟傑偡

俛俬俷俽偱亹俛俥侽侽乣亹俛俥俥俥傪巊梡

丂

丂

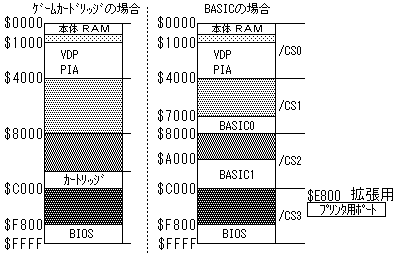

儊儌儕 儅僢僾

僋儗乕僕僠僉儞偺俼俷俵僇僙僢僩偱偡

婎斅偼傕偆堦偮俼俷俵偑嵹偣傜傟傞條偵愝寁偝傟偰偄傑偡

乛俠俽俁偲乛俠俽 俽俼俷俵偑僔儑乕僩偟偰偄傞偺偱

杮懱撪偺俛俬俷俽傪巊梡偟偰偄傑偡

俛俬俷俽偼僇乕僩儕僢僕偺桳柍栤傢偢

亹俛俥俥俠偵僕儍儞僾偟傑偡

俛俬俷俽偱亹俛俥侽侽乣亹俛俥俥俥傪巊梡

丂

丂

儊儌儕 儅僢僾

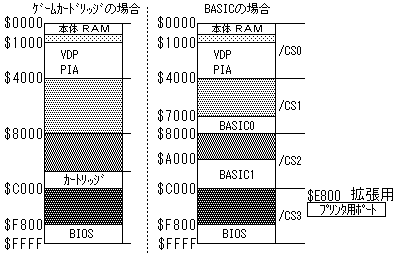

奺僩乕儞晹暘偼奺儈儔乕僀儊乕僕偵側傝傑偡

俛俙俽俬俠僾儘僌儔儉偼倁俼俙俵偵奿擺

丂

亹侽侽侽侽乣亹侽俥俥俥丗乛俠俽侽椞堟丂 杮懱撪俼俙俵 丂侾俲俛乮亹侽侽侽侽乣亹侽俁俥俥乯

亹侾侽侽侽乣亹侾俥俥俥丗俬乛俷億乕僩丂俹俬俙丂俫俢係俇俉俛俀侾俹

亹俀侽侽侽乣亹俀俥俥俥丗俬乛俷億乕僩丂俿俵俽俋俋侾俉俙儕乕僪

亹俁侽侽侽乣亹俁俥俥俥丗俬乛俷億乕僩丂俿俵俽俋俋侾俉俙儔僀僩

亹係侽侽侽乣亹俈俥俥俥丗乛俠俽侾椞堟

亹俉侽侽侽乣亹俛俥俥俥丗乛俠俽俀椞堟丂僇乕僪儕僢僕

亹俠侽侽侽乣亹俥俥俥俥丗乛俠俽俁椞堟丂杮懱撪俛俬俷俽丂俀俲俛乮亹俥俉侽侽乣亹俥俥俥俥乯

丂

丂

亙奼挘俬乛俷億乕僩亜丂

亹俤俉侽侽丂丂丂丂丂丂丗奼挘俬乛俷億乕僩丂僾儕儞僞丂僨乕僞

亹俤俉侽侾丂丂丂丂丂丂丗奼挘俬乛俷億乕僩丂僾儕儞僞丂僐儞僩儘乕儖

丂丂丂丂丂丂丂丂丂丂丂丂丂倓俈丂擖椡丂丠丠丠俼俤俙俢倄

丂

丂丂丂丂丂丂丂丂丂丂丂丂丂倓俁丂弌椡丂丠丠丠俽俿俼俷俛俤

丂

丂

亙俼俷俵僇乕僩儕僢僕亜丂

亹俛俥俤俉乣亹俛俥俤俋丗幚峴傾僪儗僗

亹俛俥俤俠丂丂丂丂丂丂丗俫俤倃偐傜俠俫俼曄姺偺儀乕僗俠俫俼僐乕僪乮傾僗僉乕僐乕僪偺応崌亹俁侽乯

亹俛俥俤俢丂丂丂丂丂丂丗

亹俛俥俤俤乣亹俛俥俤俥丗倁俼俙俵傾僪儗僗

亹俛俥俥侽乣亹俛俥俥俈丗弶婜壔倁俢俹丂俼侽乣俼俈梡僨乕僞

亹俛俥俥俉乣亹俛俥俥俋丗儊僢僙乕僕梡僨乕僞億僀儞僞

亹俛俥俥俙乣亹俛俥俥俛丗倁俼俙俵丂俥倝倢倢梡僨乕僞億僀儞僞

亹俛俥俥俠乣亹俛俥俥俢丗仸弶婜壔幚峴傾僪儗僗丂捠忢偼亹俥俉侽俉

亹俛俥俥俤乣亹俛俥俥俥丗仸俬俼俻乛俛俼俲

丂

丂丂仸婲摦帪亹俛俥俥俠乣亹俛俥俥俥偼亹侽俀侽侽乣亹侽俀侽俁偵僗僩傾偝傟

丂丂丂僐乕儖僪乛儂僢僩丂僗僞乕僩偺敾抐傪峴偄傑偡

丂

丂

亙俛俬俷俽亜

丂

亹俥俢俉俀丗儔僀僩倁俢俹僨乕僞

擖椡丗俙亖倁俢俹僨乕僞

巊梡丗俙

丂

丂倁俢俹儔僀僩億乕僩亹俁侽侽侽偵僨乕僞傪彂偒崬傒傑偡

丂

丂

亹俥俢俠係丗倁俼俙俵撉傒崬傒傾僪儗僗偺巜掕

擖椡丗亹侽侽侽係亖倁俼俙俵傾僪儗僗壓埵

丂丂丂亹侽侽侽俆亖倁俼俙俵傾僪儗僗忋埵

巊梡丗俙

丂

丂倁俼俙俵偵彂偒崬傒傪峴偆傾僪儗僗亹侽侽侽侽乣亹俁俥俥俥偺巜掕傪峴偄傑偡

亹俥俢俠俉丗倁俼俙俵彂傒崬傒傾僪儗僗偺巜掕

擖椡丗亹侽侽侽係亖倁俼俙俵傾僪儗僗壓埵

丂丂丂亹侽侽侽俆亖倁俼俙俵傾僪儗僗忋埵

巊梡丗俙

丂

丂倁俼俙俵偵彂偒崬傒傪峴偆傾僪儗僗亹侽侽侽侽乣亹俁俥俥俥偺巜掕傪峴偄傑偡

丂傾僪儗僗忋埵倓俈偲倓俇偺愝掕偼昁梫偁傝傑偣傫

丂

丂

亹俥俢俢俁丗儔僀僩倁俢俹僐儅儞僪

擖椡丗俙亖僐儅儞僪僨乕僞

巊梡丗俙

丂

丂倁俢俹儔僀僩億乕僩亹俁侽侽侾偵僨乕僞傪彂偒崬傒傑偡

丂儗僕僗僞愝掕丄傾僪儗僗愝掕偵巊梡偟傑偡

丂

丂

亹俥俤侽俥丗儕乕僪倁俼俙俵僨乕僞

巊梡丗俙

弌椡丗俙亖倁俼俙俵僨乕僞

丂

丂倁俼俙俵僨乕僞傪撉傒崬傒傑偡

丂

丂

亹俥俤侾俥丗倁俢俹丂儗僕僗僞傑偨偼傾僪儗僗偺巜掕

擖椡丗倃亖儗僕僗僞丂丂丂傑偨偼傾僪儗僗忋埵

丂丂丂俙亖儗僕僗僞僨乕僞傑偨偼傾僪儗僗壓埵

巊梡丗俙丄倃

丂

丂倁俢俹儗僕僗僞愝掕傑偨偼倁俼俙俵傾僪儗僗偺巜掕傪峴偄傑偡

丂儗僕僗僞巜掕偼偦偺傑傑偱偡偑

丂撉傒崬傓傾僪儗僗忋埵巜掕偺応崌亄亹俉侽

丂彂偒崬傓傾僪儗僗忋埵巜掕偺応崌亄亹俠侽

丂

丂亙椺亜倁俼俙俵傾僪儗僗亹侽侽侽侽偱彂偒崬傓応崌

丂丂俴俢倃丂仈亹俠侽

丂丂俴俢俙丂仈亹侽侽

丂丂俰俽俼丂亹俥俤1俥

丂

丂

亹俥俤俀俠丗俬俼俻乛俛俼俲丂乮倁俛俴俙俶俲乯

丂俬俼俻乛俛俼俲儀僋僞偱乬俰俵俹丂乮亹俛俥俥俤乯乭傪幚峴

丂捠忢偺僇乕僩儕僢僕偼亹俥俥俁俥偵僕儍儞僾偡傞

丂

丂

亹俥俤俀俥丗僛儘儁乕僕僋儕傾

巊梡丗俙丄倃

丂

丂僛儘儁乕僕亹侽侽侽侽乣亹侽侽俥俥傪亹侽侽偱僋儕傾偟傑偡

丂

丂

亹俥俤俁俉丗僉儍儔僋僞掕媊

巊梡丗俙丄倃

丂亹俥俉侽侽乣亹俥俋俥俥偺俠俧僨乕僞傪

丂倁俼俙俵亹侽俇侽侽乣亹侽俈俥俥乮俠俫俼丂亹俠侽乣亹俤俥乯偵揮憲偟傑偡

丂亹俥俉侽侽乣亹俥俋俥俥偼俠俧僨乕僞偺懠偵僾儘僌儔儉偑崿崌偝傟偰偄傞偺偱

丂慡偰掕媊偝傟偰偄傞栿偱偼偁傝傑偣傫

丂

丂

亹俥俤俆俈丗俹俽俧慡僆僼

巊梡丗俙丄倃

丂

丂亹俥俤俇俈傪僐乕儖乮俹俽俧億乕僩慖戰乯偟偰

丂俹俽俧偺壒検傪嵟彫偵偟傑偡

丂

丂

亹俥俤俇俈丗俹俽俧億乕僩慖戰

巊梡丗俙

丂

丂俹俬俙偺愙懕偝傟偰偄傞

丂俹俽俧傾僋僙僗偱巊梡偡傞堊偺愝掕傪峴偄傑偡

丂俹俽俧僨乕僞彂偒崬傒偡傞慜偵僐乕儖偟傑偡

丂

丂

亹俥俤俈俈丗俹俽俧僨乕僞彂偒崬傒

擖椡丗俙亖俹俽俧僨乕僞

弌椡丗俙亖俹俽俧僨乕僞

丂

丂俹俽俧偵僨乕僞傪彂偒崬傒丄俼俤俙俢倄偵側傞偺傑偱懸偪傑偡

丂偦偺屻拝崬傫偩億乕僩偺僨乕僞傪庢摼偟傑偡乮俙偺抣傪尦偵栠偡乯

丂

丂

丂

奺僩乕儞晹暘偼奺儈儔乕僀儊乕僕偵側傝傑偡

俛俙俽俬俠僾儘僌儔儉偼倁俼俙俵偵奿擺

丂

亹侽侽侽侽乣亹侽俥俥俥丗乛俠俽侽椞堟丂 杮懱撪俼俙俵 丂侾俲俛乮亹侽侽侽侽乣亹侽俁俥俥乯

亹侾侽侽侽乣亹侾俥俥俥丗俬乛俷億乕僩丂俹俬俙丂俫俢係俇俉俛俀侾俹

亹俀侽侽侽乣亹俀俥俥俥丗俬乛俷億乕僩丂俿俵俽俋俋侾俉俙儕乕僪

亹俁侽侽侽乣亹俁俥俥俥丗俬乛俷億乕僩丂俿俵俽俋俋侾俉俙儔僀僩

亹係侽侽侽乣亹俈俥俥俥丗乛俠俽侾椞堟

亹俉侽侽侽乣亹俛俥俥俥丗乛俠俽俀椞堟丂僇乕僪儕僢僕

亹俠侽侽侽乣亹俥俥俥俥丗乛俠俽俁椞堟丂杮懱撪俛俬俷俽丂俀俲俛乮亹俥俉侽侽乣亹俥俥俥俥乯

丂

丂

亙奼挘俬乛俷億乕僩亜丂

亹俤俉侽侽丂丂丂丂丂丂丗奼挘俬乛俷億乕僩丂僾儕儞僞丂僨乕僞

亹俤俉侽侾丂丂丂丂丂丂丗奼挘俬乛俷億乕僩丂僾儕儞僞丂僐儞僩儘乕儖

丂丂丂丂丂丂丂丂丂丂丂丂丂倓俈丂擖椡丂丠丠丠俼俤俙俢倄

丂

丂丂丂丂丂丂丂丂丂丂丂丂丂倓俁丂弌椡丂丠丠丠俽俿俼俷俛俤

丂

丂

亙俼俷俵僇乕僩儕僢僕亜丂

亹俛俥俤俉乣亹俛俥俤俋丗幚峴傾僪儗僗

亹俛俥俤俠丂丂丂丂丂丂丗俫俤倃偐傜俠俫俼曄姺偺儀乕僗俠俫俼僐乕僪乮傾僗僉乕僐乕僪偺応崌亹俁侽乯

亹俛俥俤俢丂丂丂丂丂丂丗

亹俛俥俤俤乣亹俛俥俤俥丗倁俼俙俵傾僪儗僗

亹俛俥俥侽乣亹俛俥俥俈丗弶婜壔倁俢俹丂俼侽乣俼俈梡僨乕僞

亹俛俥俥俉乣亹俛俥俥俋丗儊僢僙乕僕梡僨乕僞億僀儞僞

亹俛俥俥俙乣亹俛俥俥俛丗倁俼俙俵丂俥倝倢倢梡僨乕僞億僀儞僞

亹俛俥俥俠乣亹俛俥俥俢丗仸弶婜壔幚峴傾僪儗僗丂捠忢偼亹俥俉侽俉

亹俛俥俥俤乣亹俛俥俥俥丗仸俬俼俻乛俛俼俲

丂

丂丂仸婲摦帪亹俛俥俥俠乣亹俛俥俥俥偼亹侽俀侽侽乣亹侽俀侽俁偵僗僩傾偝傟

丂丂丂僐乕儖僪乛儂僢僩丂僗僞乕僩偺敾抐傪峴偄傑偡

丂

丂

亙俛俬俷俽亜

丂

亹俥俢俉俀丗儔僀僩倁俢俹僨乕僞

擖椡丗俙亖倁俢俹僨乕僞

巊梡丗俙

丂

丂倁俢俹儔僀僩億乕僩亹俁侽侽侽偵僨乕僞傪彂偒崬傒傑偡

丂

丂

亹俥俢俠係丗倁俼俙俵撉傒崬傒傾僪儗僗偺巜掕

擖椡丗亹侽侽侽係亖倁俼俙俵傾僪儗僗壓埵

丂丂丂亹侽侽侽俆亖倁俼俙俵傾僪儗僗忋埵

巊梡丗俙

丂

丂倁俼俙俵偵彂偒崬傒傪峴偆傾僪儗僗亹侽侽侽侽乣亹俁俥俥俥偺巜掕傪峴偄傑偡

亹俥俢俠俉丗倁俼俙俵彂傒崬傒傾僪儗僗偺巜掕

擖椡丗亹侽侽侽係亖倁俼俙俵傾僪儗僗壓埵

丂丂丂亹侽侽侽俆亖倁俼俙俵傾僪儗僗忋埵

巊梡丗俙

丂

丂倁俼俙俵偵彂偒崬傒傪峴偆傾僪儗僗亹侽侽侽侽乣亹俁俥俥俥偺巜掕傪峴偄傑偡

丂傾僪儗僗忋埵倓俈偲倓俇偺愝掕偼昁梫偁傝傑偣傫

丂

丂

亹俥俢俢俁丗儔僀僩倁俢俹僐儅儞僪

擖椡丗俙亖僐儅儞僪僨乕僞

巊梡丗俙

丂

丂倁俢俹儔僀僩億乕僩亹俁侽侽侾偵僨乕僞傪彂偒崬傒傑偡

丂儗僕僗僞愝掕丄傾僪儗僗愝掕偵巊梡偟傑偡

丂

丂

亹俥俤侽俥丗儕乕僪倁俼俙俵僨乕僞

巊梡丗俙

弌椡丗俙亖倁俼俙俵僨乕僞

丂

丂倁俼俙俵僨乕僞傪撉傒崬傒傑偡

丂

丂

亹俥俤侾俥丗倁俢俹丂儗僕僗僞傑偨偼傾僪儗僗偺巜掕

擖椡丗倃亖儗僕僗僞丂丂丂傑偨偼傾僪儗僗忋埵

丂丂丂俙亖儗僕僗僞僨乕僞傑偨偼傾僪儗僗壓埵

巊梡丗俙丄倃

丂

丂倁俢俹儗僕僗僞愝掕傑偨偼倁俼俙俵傾僪儗僗偺巜掕傪峴偄傑偡

丂儗僕僗僞巜掕偼偦偺傑傑偱偡偑

丂撉傒崬傓傾僪儗僗忋埵巜掕偺応崌亄亹俉侽

丂彂偒崬傓傾僪儗僗忋埵巜掕偺応崌亄亹俠侽

丂

丂亙椺亜倁俼俙俵傾僪儗僗亹侽侽侽侽偱彂偒崬傓応崌

丂丂俴俢倃丂仈亹俠侽

丂丂俴俢俙丂仈亹侽侽

丂丂俰俽俼丂亹俥俤1俥

丂

丂

亹俥俤俀俠丗俬俼俻乛俛俼俲丂乮倁俛俴俙俶俲乯

丂俬俼俻乛俛俼俲儀僋僞偱乬俰俵俹丂乮亹俛俥俥俤乯乭傪幚峴

丂捠忢偺僇乕僩儕僢僕偼亹俥俥俁俥偵僕儍儞僾偡傞

丂

丂

亹俥俤俀俥丗僛儘儁乕僕僋儕傾

巊梡丗俙丄倃

丂

丂僛儘儁乕僕亹侽侽侽侽乣亹侽侽俥俥傪亹侽侽偱僋儕傾偟傑偡

丂

丂

亹俥俤俁俉丗僉儍儔僋僞掕媊

巊梡丗俙丄倃

丂亹俥俉侽侽乣亹俥俋俥俥偺俠俧僨乕僞傪

丂倁俼俙俵亹侽俇侽侽乣亹侽俈俥俥乮俠俫俼丂亹俠侽乣亹俤俥乯偵揮憲偟傑偡

丂亹俥俉侽侽乣亹俥俋俥俥偼俠俧僨乕僞偺懠偵僾儘僌儔儉偑崿崌偝傟偰偄傞偺偱

丂慡偰掕媊偝傟偰偄傞栿偱偼偁傝傑偣傫

丂

丂

亹俥俤俆俈丗俹俽俧慡僆僼

巊梡丗俙丄倃

丂

丂亹俥俤俇俈傪僐乕儖乮俹俽俧億乕僩慖戰乯偟偰

丂俹俽俧偺壒検傪嵟彫偵偟傑偡

丂

丂

亹俥俤俇俈丗俹俽俧億乕僩慖戰

巊梡丗俙

丂

丂俹俬俙偺愙懕偝傟偰偄傞

丂俹俽俧傾僋僙僗偱巊梡偡傞堊偺愝掕傪峴偄傑偡

丂俹俽俧僨乕僞彂偒崬傒偡傞慜偵僐乕儖偟傑偡

丂

丂

亹俥俤俈俈丗俹俽俧僨乕僞彂偒崬傒

擖椡丗俙亖俹俽俧僨乕僞

弌椡丗俙亖俹俽俧僨乕僞

丂

丂俹俽俧偵僨乕僞傪彂偒崬傒丄俼俤俙俢倄偵側傞偺傑偱懸偪傑偡

丂偦偺屻拝崬傫偩億乕僩偺僨乕僞傪庢摼偟傑偡乮俙偺抣傪尦偵栠偡乯

丂

丂

丂

Home 傊栠傞

俵俹倀偼俇俆侽俀丂僋儘僢僋偼俀俵俫倸

俛俬俷俽偼僇乕僩儕僢僕偺抂巕傪僔儑乕僩偟偰巊梡嫋壜偟偰偄傑偡丅

丂乛俠俽侽亖亹侽仏仏仏

丂乛俠俽侾亖亹係仏仏仏

丂乛俠俽俀亖亹俉仏仏仏

丂乛俠俽俁亖亹俠仏仏仏

丂

丂

儊儌儕

俵俹倀偼俇俆侽俀丂僋儘僢僋偼俀俵俫倸

俛俬俷俽偼僇乕僩儕僢僕偺抂巕傪僔儑乕僩偟偰巊梡嫋壜偟偰偄傑偡丅

丂乛俠俽侽亖亹侽仏仏仏

丂乛俠俽侾亖亹係仏仏仏

丂乛俠俽俀亖亹俉仏仏仏

丂乛俠俽俁亖亹俠仏仏仏

丂

丂

儊儌儕

杮懱撪偵偼俀俲俛偺儅僗僋俼俷俵乮俛俬俷俽乯偲

侾俲仏係俛倝倲偺俽俼俙俵偑俀偮撪憼偝傟偰偄傑偡

俛俬俷俽偼愗傝棧偡帠傕壜擻偱偡丅

俿俵俵俁俁係俹丗俠俼俠亖們俁們俆俋侽們俇

丂

丂

俹俬俙丂俫俢係俇俉俛俀侾

杮懱撪偵偼俀俲俛偺儅僗僋俼俷俵乮俛俬俷俽乯偲

侾俲仏係俛倝倲偺俽俼俙俵偑俀偮撪憼偝傟偰偄傑偡

俛俬俷俽偼愗傝棧偡帠傕壜擻偱偡丅

俿俵俵俁俁係俹丗俠俼俠亖們俁們俆俋侽們俇

丂

丂

俹俬俙丂俫俢係俇俉俛俀侾

僉乕儃乕僪丄俹俽俧丄奼挘抂巕偼俹俬俙偱惂屼偝傟傑偡

俹俙偱僉乕儃乕僪乮僐儞僩儘乕儔乯丄奼挘抂巕偺慖戰丄

俠俛偱俹俽俧偺慖戰丄俹俛偑僨乕僞偺弌椡

奼挘抂巕偼俠俵俿偑宷偑傝傑偡

丂俤亅俀丂俹俙俈丂俼俤俙俢乛倂俼俬俿俤

丂俤亅係丂俹俙俆丂丠丠丠俼俤俵俷俿俤

丂俤亅俆丂俹俙係丂丠丠丠俼俤俵俷俿俤

丂

倁俢俹丂俿俵俽俋俋侾俉俙

僉乕儃乕僪丄俹俽俧丄奼挘抂巕偼俹俬俙偱惂屼偝傟傑偡

俹俙偱僉乕儃乕僪乮僐儞僩儘乕儔乯丄奼挘抂巕偺慖戰丄

俠俛偱俹俽俧偺慖戰丄俹俛偑僨乕僞偺弌椡

奼挘抂巕偼俠俵俿偑宷偑傝傑偡

丂俤亅俀丂俹俙俈丂俼俤俙俢乛倂俼俬俿俤

丂俤亅係丂俹俙俆丂丠丠丠俼俤俵俷俿俤

丂俤亅俆丂俹俙係丂丠丠丠俼俤俵俷俿俤

丂

倁俢俹丂俿俵俽俋俋侾俉俙

崱夞僋儘僢僋夞楬偼徣偄偰偄傑偡偑10.738俵俫倸偱偡

倁俽倄俶俠妱傝崬傒偼俬俼俻偵側傝傑偡

丂

丂

僐僱僋僞

崱夞僋儘僢僋夞楬偼徣偄偰偄傑偡偑10.738俵俫倸偱偡

倁俽倄俶俠妱傝崬傒偼俬俼俻偵側傝傑偡

丂

丂

僐僱僋僞

僇乕僩儕僢僕僐僱僋僞偱偡

俙1偑嵍忋偵側傝俛侾俉偑塃壓偵側傝傑偡

捠忢偺僎乕儉偩偲俛俬俷俽傕巊梡偡傞堊

乛俠俽俁偲乛俠俽丂俽俼俷俵偑僔儑乕僩偝傟傑偡

乛俠俽 侽偑弌偰偄傞偺偱夞楬偵傛偭偰偼

儊儌儕傗俬乛俷億乕僩偲偲偟偰巊梡壜擻偱偡

俠俲俀俷倀俿偼俀俵俫倸偱偡

丂

僎乕儉僇僙僢僩

僇乕僩儕僢僕僐僱僋僞偱偡

俙1偑嵍忋偵側傝俛侾俉偑塃壓偵側傝傑偡

捠忢偺僎乕儉偩偲俛俬俷俽傕巊梡偡傞堊

乛俠俽俁偲乛俠俽丂俽俼俷俵偑僔儑乕僩偝傟傑偡

乛俠俽 侽偑弌偰偄傞偺偱夞楬偵傛偭偰偼

儊儌儕傗俬乛俷億乕僩偲偲偟偰巊梡壜擻偱偡

俠俲俀俷倀俿偼俀俵俫倸偱偡

丂

僎乕儉僇僙僢僩

僋儗乕僕僠僉儞偺俼俷俵僇僙僢僩偱偡

婎斅偼傕偆堦偮俼俷俵偑嵹偣傜傟傞條偵愝寁偝傟偰偄傑偡

乛俠俽俁偲乛俠俽 俽俼俷俵偑僔儑乕僩偟偰偄傞偺偱

杮懱撪偺俛俬俷俽傪巊梡偟偰偄傑偡

俛俬俷俽偼僇乕僩儕僢僕偺桳柍栤傢偢

亹俛俥俥俠偵僕儍儞僾偟傑偡

俛俬俷俽偱亹俛俥侽侽乣亹俛俥俥俥傪巊梡

丂

丂

儊儌儕 儅僢僾

僋儗乕僕僠僉儞偺俼俷俵僇僙僢僩偱偡

婎斅偼傕偆堦偮俼俷俵偑嵹偣傜傟傞條偵愝寁偝傟偰偄傑偡

乛俠俽俁偲乛俠俽 俽俼俷俵偑僔儑乕僩偟偰偄傞偺偱

杮懱撪偺俛俬俷俽傪巊梡偟偰偄傑偡

俛俬俷俽偼僇乕僩儕僢僕偺桳柍栤傢偢

亹俛俥俥俠偵僕儍儞僾偟傑偡

俛俬俷俽偱亹俛俥侽侽乣亹俛俥俥俥傪巊梡

丂

丂

儊儌儕 儅僢僾

奺僩乕儞晹暘偼奺儈儔乕僀儊乕僕偵側傝傑偡

俛俙俽俬俠僾儘僌儔儉偼倁俼俙俵偵奿擺

丂

亹侽侽侽侽乣亹侽俥俥俥丗乛俠俽侽椞堟丂 杮懱撪俼俙俵 丂侾俲俛乮亹侽侽侽侽乣亹侽俁俥俥乯

亹侾侽侽侽乣亹侾俥俥俥丗俬乛俷億乕僩丂俹俬俙丂俫俢係俇俉俛俀侾俹

亹俀侽侽侽乣亹俀俥俥俥丗俬乛俷億乕僩丂俿俵俽俋俋侾俉俙儕乕僪

亹俁侽侽侽乣亹俁俥俥俥丗俬乛俷億乕僩丂俿俵俽俋俋侾俉俙儔僀僩

亹係侽侽侽乣亹俈俥俥俥丗乛俠俽侾椞堟

亹俉侽侽侽乣亹俛俥俥俥丗乛俠俽俀椞堟丂僇乕僪儕僢僕

亹俠侽侽侽乣亹俥俥俥俥丗乛俠俽俁椞堟丂杮懱撪俛俬俷俽丂俀俲俛乮亹俥俉侽侽乣亹俥俥俥俥乯

丂

丂

亙奼挘俬乛俷億乕僩亜丂

亹俤俉侽侽丂丂丂丂丂丂丗奼挘俬乛俷億乕僩丂僾儕儞僞丂僨乕僞

亹俤俉侽侾丂丂丂丂丂丂丗奼挘俬乛俷億乕僩丂僾儕儞僞丂僐儞僩儘乕儖

丂丂丂丂丂丂丂丂丂丂丂丂丂倓俈丂擖椡丂丠丠丠俼俤俙俢倄

丂

丂丂丂丂丂丂丂丂丂丂丂丂丂倓俁丂弌椡丂丠丠丠俽俿俼俷俛俤

丂

丂

亙俼俷俵僇乕僩儕僢僕亜丂

亹俛俥俤俉乣亹俛俥俤俋丗幚峴傾僪儗僗

亹俛俥俤俠丂丂丂丂丂丂丗俫俤倃偐傜俠俫俼曄姺偺儀乕僗俠俫俼僐乕僪乮傾僗僉乕僐乕僪偺応崌亹俁侽乯

亹俛俥俤俢丂丂丂丂丂丂丗

亹俛俥俤俤乣亹俛俥俤俥丗倁俼俙俵傾僪儗僗

亹俛俥俥侽乣亹俛俥俥俈丗弶婜壔倁俢俹丂俼侽乣俼俈梡僨乕僞

亹俛俥俥俉乣亹俛俥俥俋丗儊僢僙乕僕梡僨乕僞億僀儞僞

亹俛俥俥俙乣亹俛俥俥俛丗倁俼俙俵丂俥倝倢倢梡僨乕僞億僀儞僞

亹俛俥俥俠乣亹俛俥俥俢丗仸弶婜壔幚峴傾僪儗僗丂捠忢偼亹俥俉侽俉

亹俛俥俥俤乣亹俛俥俥俥丗仸俬俼俻乛俛俼俲

丂

丂丂仸婲摦帪亹俛俥俥俠乣亹俛俥俥俥偼亹侽俀侽侽乣亹侽俀侽俁偵僗僩傾偝傟

丂丂丂僐乕儖僪乛儂僢僩丂僗僞乕僩偺敾抐傪峴偄傑偡

丂

丂

亙俛俬俷俽亜

丂

亹俥俢俉俀丗儔僀僩倁俢俹僨乕僞

擖椡丗俙亖倁俢俹僨乕僞

巊梡丗俙

丂

丂倁俢俹儔僀僩億乕僩亹俁侽侽侽偵僨乕僞傪彂偒崬傒傑偡

丂

丂

亹俥俢俠係丗倁俼俙俵撉傒崬傒傾僪儗僗偺巜掕

擖椡丗亹侽侽侽係亖倁俼俙俵傾僪儗僗壓埵

丂丂丂亹侽侽侽俆亖倁俼俙俵傾僪儗僗忋埵

巊梡丗俙

丂

丂倁俼俙俵偵彂偒崬傒傪峴偆傾僪儗僗亹侽侽侽侽乣亹俁俥俥俥偺巜掕傪峴偄傑偡

亹俥俢俠俉丗倁俼俙俵彂傒崬傒傾僪儗僗偺巜掕

擖椡丗亹侽侽侽係亖倁俼俙俵傾僪儗僗壓埵

丂丂丂亹侽侽侽俆亖倁俼俙俵傾僪儗僗忋埵

巊梡丗俙

丂

丂倁俼俙俵偵彂偒崬傒傪峴偆傾僪儗僗亹侽侽侽侽乣亹俁俥俥俥偺巜掕傪峴偄傑偡

丂傾僪儗僗忋埵倓俈偲倓俇偺愝掕偼昁梫偁傝傑偣傫

丂

丂

亹俥俢俢俁丗儔僀僩倁俢俹僐儅儞僪

擖椡丗俙亖僐儅儞僪僨乕僞

巊梡丗俙

丂

丂倁俢俹儔僀僩億乕僩亹俁侽侽侾偵僨乕僞傪彂偒崬傒傑偡

丂儗僕僗僞愝掕丄傾僪儗僗愝掕偵巊梡偟傑偡

丂

丂

亹俥俤侽俥丗儕乕僪倁俼俙俵僨乕僞

巊梡丗俙

弌椡丗俙亖倁俼俙俵僨乕僞

丂

丂倁俼俙俵僨乕僞傪撉傒崬傒傑偡

丂

丂

亹俥俤侾俥丗倁俢俹丂儗僕僗僞傑偨偼傾僪儗僗偺巜掕

擖椡丗倃亖儗僕僗僞丂丂丂傑偨偼傾僪儗僗忋埵

丂丂丂俙亖儗僕僗僞僨乕僞傑偨偼傾僪儗僗壓埵

巊梡丗俙丄倃

丂

丂倁俢俹儗僕僗僞愝掕傑偨偼倁俼俙俵傾僪儗僗偺巜掕傪峴偄傑偡

丂儗僕僗僞巜掕偼偦偺傑傑偱偡偑

丂撉傒崬傓傾僪儗僗忋埵巜掕偺応崌亄亹俉侽

丂彂偒崬傓傾僪儗僗忋埵巜掕偺応崌亄亹俠侽

丂

丂亙椺亜倁俼俙俵傾僪儗僗亹侽侽侽侽偱彂偒崬傓応崌

丂丂俴俢倃丂仈亹俠侽

丂丂俴俢俙丂仈亹侽侽

丂丂俰俽俼丂亹俥俤1俥

丂

丂

亹俥俤俀俠丗俬俼俻乛俛俼俲丂乮倁俛俴俙俶俲乯

丂俬俼俻乛俛俼俲儀僋僞偱乬俰俵俹丂乮亹俛俥俥俤乯乭傪幚峴

丂捠忢偺僇乕僩儕僢僕偼亹俥俥俁俥偵僕儍儞僾偡傞

丂

丂

亹俥俤俀俥丗僛儘儁乕僕僋儕傾

巊梡丗俙丄倃

丂

丂僛儘儁乕僕亹侽侽侽侽乣亹侽侽俥俥傪亹侽侽偱僋儕傾偟傑偡

丂

丂

亹俥俤俁俉丗僉儍儔僋僞掕媊

巊梡丗俙丄倃

丂亹俥俉侽侽乣亹俥俋俥俥偺俠俧僨乕僞傪

丂倁俼俙俵亹侽俇侽侽乣亹侽俈俥俥乮俠俫俼丂亹俠侽乣亹俤俥乯偵揮憲偟傑偡

丂亹俥俉侽侽乣亹俥俋俥俥偼俠俧僨乕僞偺懠偵僾儘僌儔儉偑崿崌偝傟偰偄傞偺偱

丂慡偰掕媊偝傟偰偄傞栿偱偼偁傝傑偣傫

丂

丂

亹俥俤俆俈丗俹俽俧慡僆僼

巊梡丗俙丄倃

丂

丂亹俥俤俇俈傪僐乕儖乮俹俽俧億乕僩慖戰乯偟偰

丂俹俽俧偺壒検傪嵟彫偵偟傑偡

丂

丂

亹俥俤俇俈丗俹俽俧億乕僩慖戰

巊梡丗俙

丂

丂俹俬俙偺愙懕偝傟偰偄傞

丂俹俽俧傾僋僙僗偱巊梡偡傞堊偺愝掕傪峴偄傑偡

丂俹俽俧僨乕僞彂偒崬傒偡傞慜偵僐乕儖偟傑偡

丂

丂

亹俥俤俈俈丗俹俽俧僨乕僞彂偒崬傒

擖椡丗俙亖俹俽俧僨乕僞

弌椡丗俙亖俹俽俧僨乕僞

丂

丂俹俽俧偵僨乕僞傪彂偒崬傒丄俼俤俙俢倄偵側傞偺傑偱懸偪傑偡

丂偦偺屻拝崬傫偩億乕僩偺僨乕僞傪庢摼偟傑偡乮俙偺抣傪尦偵栠偡乯

丂

丂

丂

奺僩乕儞晹暘偼奺儈儔乕僀儊乕僕偵側傝傑偡

俛俙俽俬俠僾儘僌儔儉偼倁俼俙俵偵奿擺

丂

亹侽侽侽侽乣亹侽俥俥俥丗乛俠俽侽椞堟丂 杮懱撪俼俙俵 丂侾俲俛乮亹侽侽侽侽乣亹侽俁俥俥乯

亹侾侽侽侽乣亹侾俥俥俥丗俬乛俷億乕僩丂俹俬俙丂俫俢係俇俉俛俀侾俹

亹俀侽侽侽乣亹俀俥俥俥丗俬乛俷億乕僩丂俿俵俽俋俋侾俉俙儕乕僪

亹俁侽侽侽乣亹俁俥俥俥丗俬乛俷億乕僩丂俿俵俽俋俋侾俉俙儔僀僩

亹係侽侽侽乣亹俈俥俥俥丗乛俠俽侾椞堟

亹俉侽侽侽乣亹俛俥俥俥丗乛俠俽俀椞堟丂僇乕僪儕僢僕

亹俠侽侽侽乣亹俥俥俥俥丗乛俠俽俁椞堟丂杮懱撪俛俬俷俽丂俀俲俛乮亹俥俉侽侽乣亹俥俥俥俥乯

丂

丂

亙奼挘俬乛俷億乕僩亜丂

亹俤俉侽侽丂丂丂丂丂丂丗奼挘俬乛俷億乕僩丂僾儕儞僞丂僨乕僞

亹俤俉侽侾丂丂丂丂丂丂丗奼挘俬乛俷億乕僩丂僾儕儞僞丂僐儞僩儘乕儖

丂丂丂丂丂丂丂丂丂丂丂丂丂倓俈丂擖椡丂丠丠丠俼俤俙俢倄

丂

丂丂丂丂丂丂丂丂丂丂丂丂丂倓俁丂弌椡丂丠丠丠俽俿俼俷俛俤

丂

丂

亙俼俷俵僇乕僩儕僢僕亜丂

亹俛俥俤俉乣亹俛俥俤俋丗幚峴傾僪儗僗

亹俛俥俤俠丂丂丂丂丂丂丗俫俤倃偐傜俠俫俼曄姺偺儀乕僗俠俫俼僐乕僪乮傾僗僉乕僐乕僪偺応崌亹俁侽乯

亹俛俥俤俢丂丂丂丂丂丂丗

亹俛俥俤俤乣亹俛俥俤俥丗倁俼俙俵傾僪儗僗

亹俛俥俥侽乣亹俛俥俥俈丗弶婜壔倁俢俹丂俼侽乣俼俈梡僨乕僞

亹俛俥俥俉乣亹俛俥俥俋丗儊僢僙乕僕梡僨乕僞億僀儞僞

亹俛俥俥俙乣亹俛俥俥俛丗倁俼俙俵丂俥倝倢倢梡僨乕僞億僀儞僞

亹俛俥俥俠乣亹俛俥俥俢丗仸弶婜壔幚峴傾僪儗僗丂捠忢偼亹俥俉侽俉

亹俛俥俥俤乣亹俛俥俥俥丗仸俬俼俻乛俛俼俲

丂

丂丂仸婲摦帪亹俛俥俥俠乣亹俛俥俥俥偼亹侽俀侽侽乣亹侽俀侽俁偵僗僩傾偝傟

丂丂丂僐乕儖僪乛儂僢僩丂僗僞乕僩偺敾抐傪峴偄傑偡

丂

丂

亙俛俬俷俽亜

丂

亹俥俢俉俀丗儔僀僩倁俢俹僨乕僞

擖椡丗俙亖倁俢俹僨乕僞

巊梡丗俙

丂

丂倁俢俹儔僀僩億乕僩亹俁侽侽侽偵僨乕僞傪彂偒崬傒傑偡

丂

丂

亹俥俢俠係丗倁俼俙俵撉傒崬傒傾僪儗僗偺巜掕

擖椡丗亹侽侽侽係亖倁俼俙俵傾僪儗僗壓埵

丂丂丂亹侽侽侽俆亖倁俼俙俵傾僪儗僗忋埵

巊梡丗俙

丂

丂倁俼俙俵偵彂偒崬傒傪峴偆傾僪儗僗亹侽侽侽侽乣亹俁俥俥俥偺巜掕傪峴偄傑偡

亹俥俢俠俉丗倁俼俙俵彂傒崬傒傾僪儗僗偺巜掕

擖椡丗亹侽侽侽係亖倁俼俙俵傾僪儗僗壓埵

丂丂丂亹侽侽侽俆亖倁俼俙俵傾僪儗僗忋埵

巊梡丗俙

丂

丂倁俼俙俵偵彂偒崬傒傪峴偆傾僪儗僗亹侽侽侽侽乣亹俁俥俥俥偺巜掕傪峴偄傑偡

丂傾僪儗僗忋埵倓俈偲倓俇偺愝掕偼昁梫偁傝傑偣傫

丂

丂

亹俥俢俢俁丗儔僀僩倁俢俹僐儅儞僪

擖椡丗俙亖僐儅儞僪僨乕僞

巊梡丗俙

丂

丂倁俢俹儔僀僩億乕僩亹俁侽侽侾偵僨乕僞傪彂偒崬傒傑偡

丂儗僕僗僞愝掕丄傾僪儗僗愝掕偵巊梡偟傑偡

丂

丂

亹俥俤侽俥丗儕乕僪倁俼俙俵僨乕僞

巊梡丗俙

弌椡丗俙亖倁俼俙俵僨乕僞

丂

丂倁俼俙俵僨乕僞傪撉傒崬傒傑偡

丂

丂

亹俥俤侾俥丗倁俢俹丂儗僕僗僞傑偨偼傾僪儗僗偺巜掕

擖椡丗倃亖儗僕僗僞丂丂丂傑偨偼傾僪儗僗忋埵

丂丂丂俙亖儗僕僗僞僨乕僞傑偨偼傾僪儗僗壓埵

巊梡丗俙丄倃

丂

丂倁俢俹儗僕僗僞愝掕傑偨偼倁俼俙俵傾僪儗僗偺巜掕傪峴偄傑偡

丂儗僕僗僞巜掕偼偦偺傑傑偱偡偑

丂撉傒崬傓傾僪儗僗忋埵巜掕偺応崌亄亹俉侽

丂彂偒崬傓傾僪儗僗忋埵巜掕偺応崌亄亹俠侽

丂

丂亙椺亜倁俼俙俵傾僪儗僗亹侽侽侽侽偱彂偒崬傓応崌

丂丂俴俢倃丂仈亹俠侽

丂丂俴俢俙丂仈亹侽侽

丂丂俰俽俼丂亹俥俤1俥

丂

丂

亹俥俤俀俠丗俬俼俻乛俛俼俲丂乮倁俛俴俙俶俲乯

丂俬俼俻乛俛俼俲儀僋僞偱乬俰俵俹丂乮亹俛俥俥俤乯乭傪幚峴

丂捠忢偺僇乕僩儕僢僕偼亹俥俥俁俥偵僕儍儞僾偡傞

丂

丂

亹俥俤俀俥丗僛儘儁乕僕僋儕傾

巊梡丗俙丄倃

丂

丂僛儘儁乕僕亹侽侽侽侽乣亹侽侽俥俥傪亹侽侽偱僋儕傾偟傑偡

丂

丂

亹俥俤俁俉丗僉儍儔僋僞掕媊

巊梡丗俙丄倃

丂亹俥俉侽侽乣亹俥俋俥俥偺俠俧僨乕僞傪

丂倁俼俙俵亹侽俇侽侽乣亹侽俈俥俥乮俠俫俼丂亹俠侽乣亹俤俥乯偵揮憲偟傑偡

丂亹俥俉侽侽乣亹俥俋俥俥偼俠俧僨乕僞偺懠偵僾儘僌儔儉偑崿崌偝傟偰偄傞偺偱

丂慡偰掕媊偝傟偰偄傞栿偱偼偁傝傑偣傫

丂

丂

亹俥俤俆俈丗俹俽俧慡僆僼

巊梡丗俙丄倃

丂

丂亹俥俤俇俈傪僐乕儖乮俹俽俧億乕僩慖戰乯偟偰

丂俹俽俧偺壒検傪嵟彫偵偟傑偡

丂

丂

亹俥俤俇俈丗俹俽俧億乕僩慖戰

巊梡丗俙

丂

丂俹俬俙偺愙懕偝傟偰偄傞

丂俹俽俧傾僋僙僗偱巊梡偡傞堊偺愝掕傪峴偄傑偡

丂俹俽俧僨乕僞彂偒崬傒偡傞慜偵僐乕儖偟傑偡

丂

丂

亹俥俤俈俈丗俹俽俧僨乕僞彂偒崬傒

擖椡丗俙亖俹俽俧僨乕僞

弌椡丗俙亖俹俽俧僨乕僞

丂

丂俹俽俧偵僨乕僞傪彂偒崬傒丄俼俤俙俢倄偵側傞偺傑偱懸偪傑偡

丂偦偺屻拝崬傫偩億乕僩偺僨乕僞傪庢摼偟傑偡乮俙偺抣傪尦偵栠偡乯

丂

丂

丂